- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98143 > SSTUG32865ET/S (NXP SEMICONDUCTORS) SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 PDF資料下載

參數(shù)資料

| 型號: | SSTUG32865ET/S |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 鎖存器 |

| 英文描述: | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

| 封裝: | 9 X 13 MM, 0.70 MM PITCH, LEAD FREE, PLASTIC, SOT-802-2, TFBGA-160 |

| 文件頁數(shù): | 8/28頁 |

| 文件大小: | 154K |

| 代理商: | SSTUG32865ET/S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

SSTUG32865_1

NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 01 — 16 August 2007

16 of 28

NXP Semiconductors

SSTUG32865

1.8 V DDR2-1G registered buffer with parity

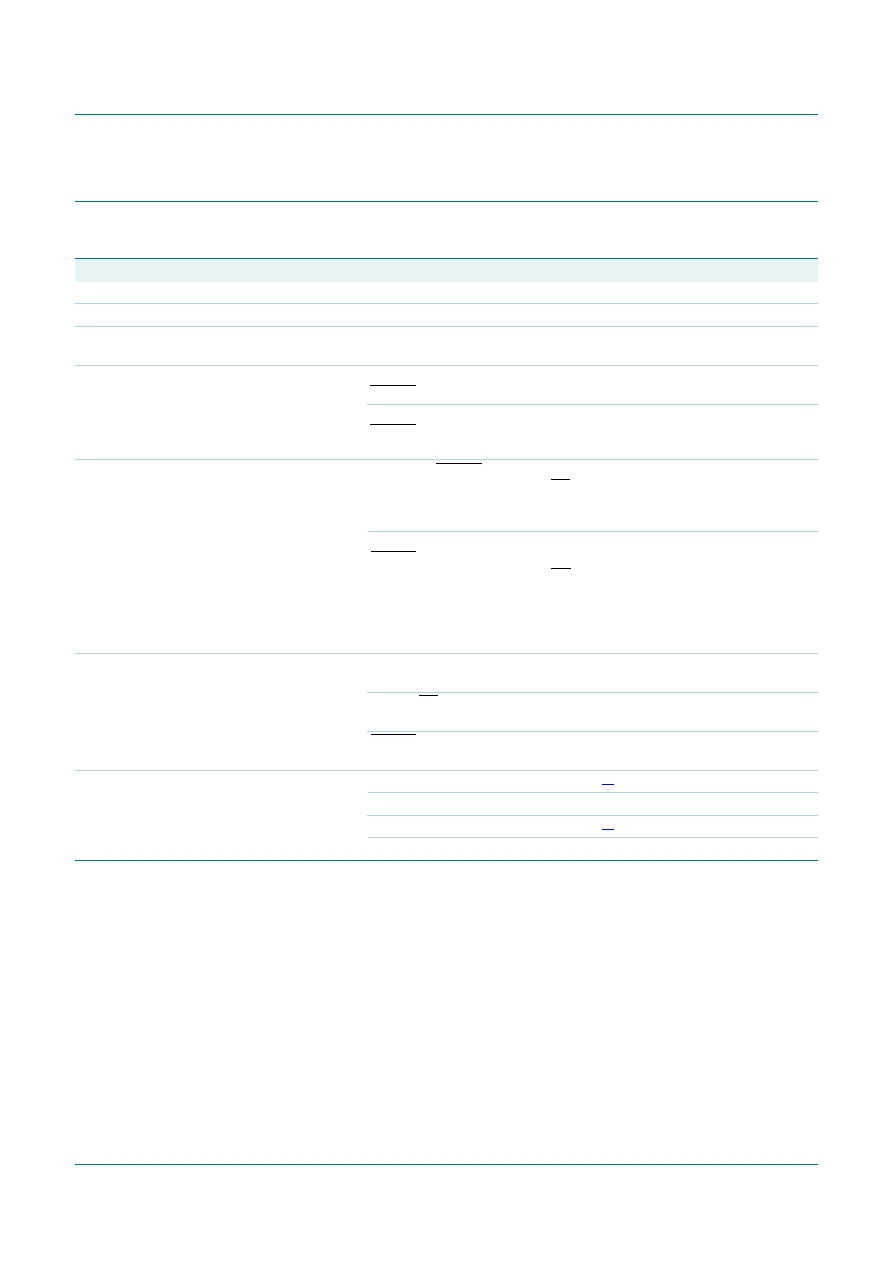

10. Characteristics

[1]

Instantaneous is dened as within < 2 ns following the output data transition edge.

Table 10.

Characteristics

Over recommended operating conditions, unless otherwise noted.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VOH

HIGH-level output voltage

IOH = 6 mA; VDD = 1.7 V

1.2

-

V

VOL

LOW-level output voltage

IOL = 6 mA; VDD = 1.7 V

-

0.5

V

II

input current

all inputs; VI =VDD or GND;

VDD = 2.0 V

--

±5

A

IDD

supply current

static standby current;

RESET = GND; VDD = 2.0 V

--

2

mA

static operating current;

RESET = VDD; VDD = 2.0 V;

VI =VIH(AC) or VIL(AC)

-

40

mA

IDDD

dynamic operating current per MHz clock only; RESET = VDD;

VI =VIH(AC) or VIL(AC); CK and CK

switching at 50 % duty cycle.

IO = 0 mA; VDD = 1.8 V

-16

-

A

per each data input;

RESET = VDD;

VI =VIH(AC) or VIL(AC); CK and CK

switching at 50 % duty cycle. One

data input switching at half clock

frequency, 50 % duty cycle.

IO = 0 mA; VDD = 1.8 V

-19

-

A

Ci

input capacitance

data inputs; VI =Vref ± 250 mV;

VDD = 1.8 V

2.5

-

3.5

pF

CK and CK; VICR = 0.9 V;

VID = 600 mV; VDD = 1.8 V

2-

3

pF

RESET; VI =VDD or GND;

VDD = 1.8 V

3-

5

pF

Zo

output impedance

normal drive; instantaneous

[1] -15

-

normal drive; steady-state

-

53

-

high drive; instantaneous

[1] -7

-

high drive; steady-state

-

53

-

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SSTUG32868ET/G | 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA176 |

| SSTUP32866EC/S | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTV16857EC | POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA56 |

| SSTV16859DGG,118 | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

| SSTV16859BS,118 | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PQCC56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SSTUG32866 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer |

| SSTUG32866EC/G | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer |

| SSTUG32866EC/G,518 | 功能描述:寄存器 1.8V REG RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時鐘頻率:36 MHz 傳播延遲時間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTUG32866EC/G-T | 功能描述:寄存器 1.8V REG BUF/PARITY-DDR2-1G RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時鐘頻率:36 MHz 傳播延遲時間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTUG32866EC/S | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。