- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98143 > SSTUG32865ET/S (NXP SEMICONDUCTORS) SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 PDF資料下載

參數(shù)資料

| 型號(hào): | SSTUG32865ET/S |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 鎖存器 |

| 英文描述: | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA160 |

| 封裝: | 9 X 13 MM, 0.70 MM PITCH, LEAD FREE, PLASTIC, SOT-802-2, TFBGA-160 |

| 文件頁(yè)數(shù): | 10/28頁(yè) |

| 文件大?。?/td> | 154K |

| 代理商: | SSTUG32865ET/S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

SSTUG32865_1

NXP B.V. 2007. All rights reserved.

Product data sheet

Rev. 01 — 16 August 2007

18 of 28

NXP Semiconductors

SSTUG32865

1.8 V DDR2-1G registered buffer with parity

11. Test information

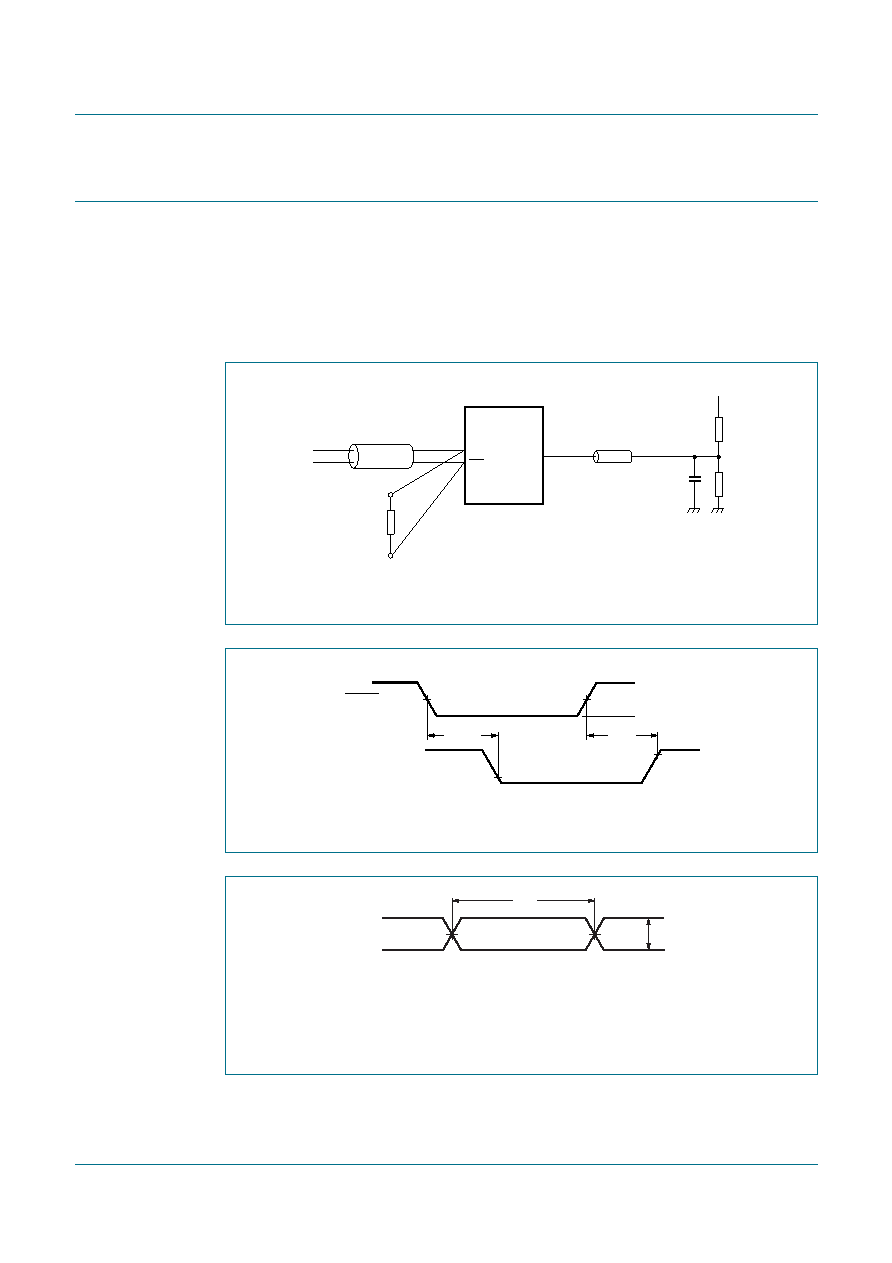

11.1 Test circuit

All input pulses are supplied by generators having the following characteristics:

Pulse Repetition Rate (PRR)

≤ 10 MHz; Z

0 =50 ; input slew rate = 1 V/ns ± 20 %,

unless otherwise specied.

The outputs are measured one at a time with one transition per measurement.

(1) CL includes probe and jig capacitance.

Fig 8.

Load circuit

(1) IDD tested with clock and data inputs held at VDD or GND, and IO = 0 mA.

Fig 9.

Voltage and current waveforms; inputs active and inactive times

VID = 600 mV.

VIH =Vref + 250 mV (AC voltage levels) for differential inputs. VIH =VDD for LVCMOS inputs.

VIL =Vref 250 mV (AC voltage levels) for differential inputs. VIL = GND for LVCMOS inputs.

Fig 10. Voltage waveforms; pulse duration

RL = 100

RL = 1000

VDD

50

CK inputs

CK

OUT

DUT

test point

002aaa371

test point

delay = 350 ps

Zo = 50

RL = 1000

CL = 30 pF(1)

LVCMOS

RESET

10 %

IDD(1)

tINACT

VDD

0.5VDD

tACT

90 %

0 V

002aaa372

0.5VDD

VICR

VIH

VIL

input

tW

VID

002aaa373

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SSTUG32868ET/G | 32868 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA176 |

| SSTUP32866EC/S | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTV16857EC | POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA56 |

| SSTV16859DGG,118 | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO64 |

| SSTV16859BS,118 | SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PQCC56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SSTUG32866 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer |

| SSTUG32866EC/G | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer |

| SSTUG32866EC/G,518 | 功能描述:寄存器 1.8V REG RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTUG32866EC/G-T | 功能描述:寄存器 1.8V REG BUF/PARITY-DDR2-1G RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTUG32866EC/S | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered buffer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。