- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365666 > SN74V3680-10PEU (Texas Instruments, Inc.) 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES PDF資料下載

參數(shù)資料

| 型號(hào): | SN74V3680-10PEU |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| 中文描述: | 的3.3V的CMOS先入先出存儲(chǔ)器 |

| 文件頁數(shù): | 19/50頁 |

| 文件大小: | 729K |

| 代理商: | SN74V3680-10PEU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

SN74V3640, SN74V3650, SN74V3660, SN74V3670, SN74V3680, SN74V3690

1024

×

36, 2048

×

36, 4096

×

36, 8192

×

36, 16384

×

36, 32768

×

36

3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES

SCAS668A

–

NOVEMBER 2001

–

REVISED MARCH 2003

19

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

synchronous vs asynchronous programmable flag timing selection

The SN74V3640, SN74V3650, SN74V3660, SN74V3670, SN74V3680, and SN74V3690 can be configured

during the master reset cycle, with either synchronous or asynchronous timing for PAF and PAE, by use of the

PFM pin.

If synchronous PAF/PAE configuration is selected (PFM high during MRS), PAF is asserted and updated on the

rising edge of WCLK only and not RCLK. Similarly, PAE is asserted and updated on the rising edge of RCLK

only, and not WCLK (see Figure 17 for synchronous PAF timing and Figure 18 for synchronous PAE timing).

If asynchronous PAF/PAE configuration is selected (PFM low during MRS), PAF is asserted low on the

low-to-high transition of WCLK, and PAF is reset to high on the low-to-high transition of RCLK. Similarly, PAE

is asserted low on the low-to-high transition of RCLK. PAE is reset to high on the low-to-high transition of WCLK.

See Figure 19 for asynchronous PAF timing and Figure 20 for asynchronous PAE timing.

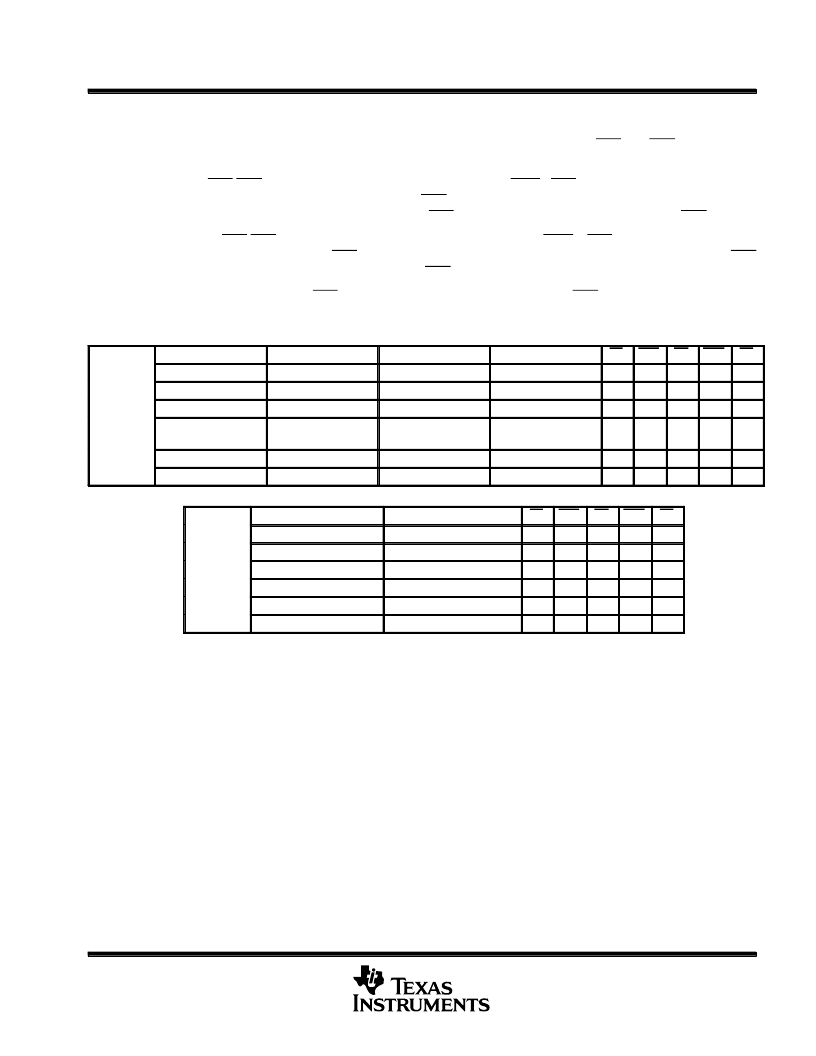

Table 3. Status Flags for Standard Mode

SN74V3640

0

SN74V3650

0

SN74V3660

0

SN74V3670

0

FF

H

PAF

H

HF

H

PAE

L

EF

L

Number of

Words in

FIFO (see

Note 8)

1 to n

1 to n

1 to n

1 to n

H

H

H

L

H

(n + 1) to 512

(n + 1) to 1024

(n + 1) to 2048

(n + 1) to 4096

H

H

H

H

H

513 to

[1024

–

(m + 1)]

1025 to

[2048

–

(m + 1)]

2049 to

[4096

–

(m + 1)]

4097 to

[8192

–

(m + 1)]

H

H

L

H

H

(1024

–

m) to 1023

1024

(2048

–

m) to 2047

2048

(4096

–

m) to 4095

4096

(8192

–

m) to 8191

8192

H

L

L

L

L

L

H

H

H

H

SN74V3680

SN74V3690

FF

PAF

HF

PAE

EF

0

0

H

H

H

L

L

Number of

d i

Words in

FIFO (see

Note 8)

1 to n

1 to n

H

H

H

L

H

(n + 1) to 8192

(n + 1) to 16384

H

H

H

H

H

8193 to [16384

–

(m + 1)]

16385 to [32768

–

(m + 1)]

H

H

L

H

H

(16384

–

m) to 16383

16384

(32768

–

m) to 32767

32768

H

L

L

L

L

L

H

H

H

H

NOTE 8: See Table 2 for values for n, m.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74V3640-10PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3640-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3650-10PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3650-15PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

| SN74V3650-6PEU | 3.3-V CMOS FIRST-IN, FIRST-OUT MEMORIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74V3680-15PEU | 功能描述:先進(jìn)先出 16384 x 36 Synch 先進(jìn)先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲(chǔ)容量:4 Mbit 定時(shí)類型:Synchronous 組織:256 K x 18 最大時(shí)鐘頻率:100 MHz 訪問時(shí)間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74V3680-6PEU | 功能描述:先進(jìn)先出 16384 x 36 Synch 先進(jìn)先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲(chǔ)容量:4 Mbit 定時(shí)類型:Synchronous 組織:256 K x 18 最大時(shí)鐘頻率:100 MHz 訪問時(shí)間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74V3680-7PEU | 功能描述:先進(jìn)先出 16384 x 36 Synch 先進(jìn)先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲(chǔ)容量:4 Mbit 定時(shí)類型:Synchronous 組織:256 K x 18 最大時(shí)鐘頻率:100 MHz 訪問時(shí)間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74V3690-10PEU | 功能描述:先進(jìn)先出 32768 x 36 Synch 先進(jìn)先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲(chǔ)容量:4 Mbit 定時(shí)類型:Synchronous 組織:256 K x 18 最大時(shí)鐘頻率:100 MHz 訪問時(shí)間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

| SN74V3690-15PEU | 功能描述:先進(jìn)先出 32768 x 36 Synch 先進(jìn)先出 Memory RoHS:否 制造商:IDT 電路數(shù)量: 數(shù)據(jù)總線寬度:18 bit 總線定向:Unidirectional 存儲(chǔ)容量:4 Mbit 定時(shí)類型:Synchronous 組織:256 K x 18 最大時(shí)鐘頻率:100 MHz 訪問時(shí)間:10 ns 電源電壓-最大:3.6 V 電源電壓-最小:6 V 最大工作電流:35 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-80 封裝: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。