- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378699 > SM8212 (Seiko NPC Corporation) POCSAG Decoder For Multiframe Pagers PDF資料下載

參數(shù)資料

| 型號: | SM8212 |

| 廠商: | Seiko NPC Corporation |

| 英文描述: | POCSAG Decoder For Multiframe Pagers |

| 中文描述: | POCSAG碼解碼器多幀尋呼機(jī) |

| 文件頁數(shù): | 10/32頁 |

| 文件大?。?/td> | 167K |

| 代理商: | SM8212 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

NIPPON PRECISION CIRCUITS-10

SM8212B

The SM8212B controls the intermittent-duty operation

of the RF stage, which reduces battery consumption, and

outputs three control signals (BS1, BS2, BS3). The func-

tion each signal controls in each mode is described below.

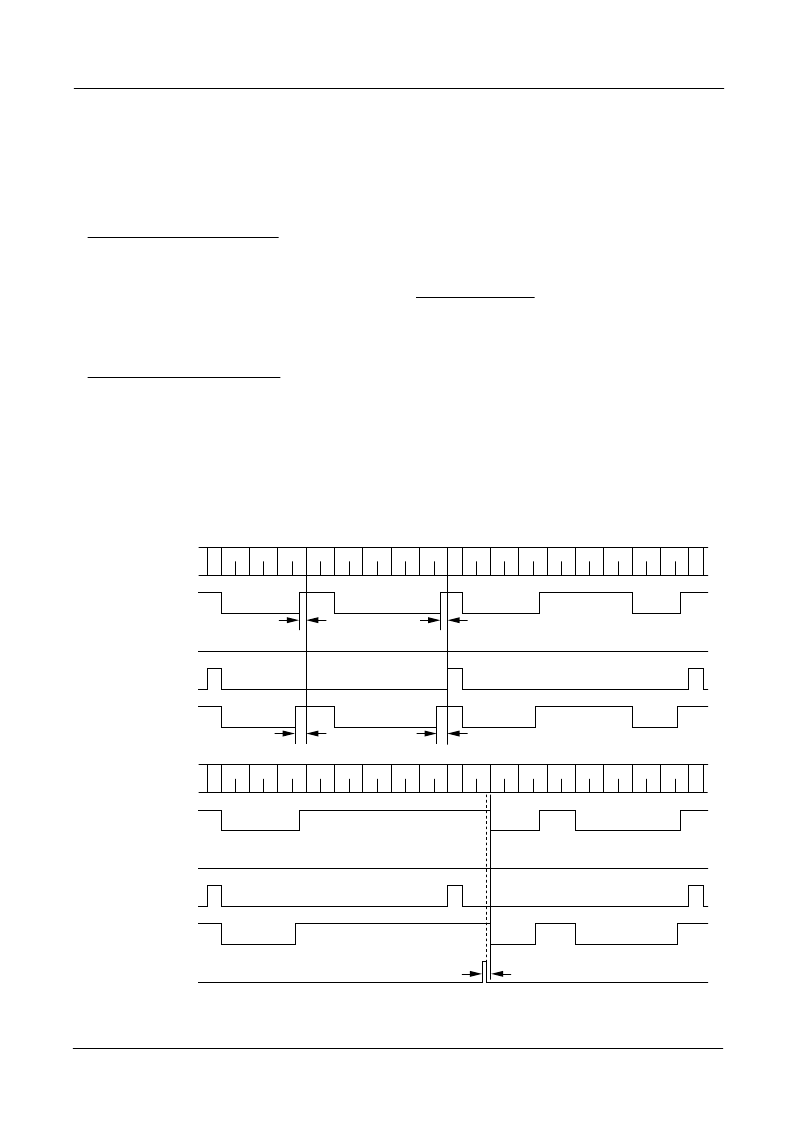

BS1 (RF-control main output signal)

The RF stage is active when BS1 is HIGH. The ris-

ing-edge setup time for receive timing is set by flags

RF0 to RF5 (61 steps). The maximum setup time is

25.417 ms at 2400 bps, 50.833 ms at 1200 bps and

119.141 ms at 512 bps. Note that 3E and 3F are

invalid settings for BS1.

BS2 (RF DC-level adjustment signal)

BS2 is used to control the discharge of the receive sig-

nal DC-cut capacitor. The function of BS2 is deter-

mined by flag BS2, as described below.

-When flag “BS2 option” is 0, pin BS2 goes HIGH

together with BS1 and then goes LOW again after the

BS1 setup time in idle mode. In preamble and lock

(during address/message reception) mode, it keeps

LOW.

-When flag “BS2 option” is 1, pin BS2 goes HIGH

during lock mode sync code receive timing and idle

mode signal receive timing. In preamble mode, it

keeps LOW.

BS3 (PLL setup signal)

BS3 is used to control PLL operation when the PLL is

used. The rising-edge setup time for receive timing is

set by flags PL0 to PL5 (61 steps). The maximum

setup time is 25.833 ms at 2400 bps, 51.667 ms at

1200 bps and 121.094 ms at 512 bps. Note that 3F is

an invalid setting for BS3.

Note also that the setup times should be set such that

(BS3 rising-edge setup time) > (BS1 rising-edge setup

time).

2. Battery Saving (BS1, BS2, BS3)

S

I

M

A

I

M

I

A

M

M

M

M

I

I

I

A

M

S

M

M

M

M

I

I

A

Self address

M

M

M

M

I

A

M

S

A

M

0

1

2

3

4

5

6

7

0

1

3

4

5

6

7

2

0

1

2

3

4

5

6

7

0

1

3

4

5

6

7

2

S

M

A

S

M

M

I

I

I

I

M

M

M

M

M

M

M

M

S

M

M

M

I

A

M

M

M

I

A

M

I

I

I

M

M

Self address

1.953*Nms (0.833*Nms)

[0.417*Nms]

1.953*Mms

(0.833*Mms) [0.417*Mms]

1.953*Nms (0.833*Nms)

[0.417*Nms]

1.953*Mms

(0.833*Mms) [0.417*Mms]

BREAK detection to reception stop (32 bit max.)

Receive code

BS1

BREAK command

BS2

(flag BS2 option = 0)

BS2

(flag BS2 option = 1)

BS3

Receive code

BS1

BS2

(flag BS2 option = 0)

BS2

(flag BS2 option = 1)

BS3

Figure 3. BS1, BS2 and BS3 timing (LOCK mode, frame 3)

Address does not match

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SM8212B | POCSAG Decoder For Multiframe Pagers |

| SM8213 | MINIATURE POWER RELAY |

| SM8213AM | POCSAG Decoder For Multiframe Pagers |

| SM8220 | Calling Number Identification Receiver IC |

| SM8221 | Calling Number Identification Receiver IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SM8212B | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:POCSAG Decoder For Multiframe Pagers |

| SM8213 | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:POCSAG Decoder For Multiframe Pagers |

| SM8213AM | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:POCSAG Decoder For Multiframe Pagers |

| SM821C906ZAA | 制造商:AVX Corporation 功能描述:- Bulk |

| SM8220 | 制造商:NPC 制造商全稱:Nippon Precision Circuits Inc 功能描述:Calling Number Identification Receiver IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。