- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373395 > Si5022-BM (Electronic Theatre Controls, Inc.) MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP PDF資料下載

參數(shù)資料

| 型號: | Si5022-BM |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 運動控制電子 |

| 英文描述: | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| 中文描述: | 多速率SONET / SDH的CDR集成電路限幅放大器 |

| 文件頁數(shù): | 11/22頁 |

| 文件大小: | 399K |

| 代理商: | SI5022-BM |

Si5022/Si5023

Preliminary Rev. 0.46

11

Functional Description

The Si5022/23 integrates a high-speed limiting amplifier

(LA) with a multi-rate clock and data recovery unit

(CDR) that operates up to 2.7 Gbps. No external

reference clock is required for clock and data recovery.

The limiting amplifier magnifies very low-level input data

signals so that accurate clock and data recovery can be

performed. The CDR uses Silicon Laboratories’ DSPLL

technology to recover a clock synchronous to the input

data stream. The recovered clock is used to retime the

incoming data, and both are output synchronously via

current-mode logic (CML) drivers. Silicon Laboratories’

DSPLL technology ensures superior jitter performance

while eliminating the need for external loop filter

components found in traditional phase-lock loop

implementations.

The limiting amplifier includes a control input for

adjusting the 0/1 data slicing level and provides a loss-

of-signal level alarm output. The CDR includes a bit-

error-rate performance monitor which signals a high bit-

error-rate

condition

(associated

incoming jitter) relative to an externally adjustable bit-

error-rate threshold.

The optional reference clock minimizes the CDR

acquisition time and provides a stable reference for

maintaining the output clock when locking to reference

is desired.

Limiting Amplifier

The limiting amplifier accepts the low-level signal output

from a transimpedance amplifier (TIA). The low-level

signal is amplified to a usable level for the clock and

data recovery unit. The minimum input swing

requirement is specified in Table 2. Larger input

amplitudes (up to the maximum input swing specified in

Table 2) are accommodated without degradation of

performance. The limiting amplifier ensures optimal

data slicing by using a digital dc offset cancellation

technique to remove any dc bias introduced by the

amplification stage.

with

excessive

DSPLL

The Si5022/23 PLL structure (shown in Figure 1 on

page 4) utilizes Silicon Laboratories' DSPLL technology

to maintain superior jitter performance while eliminating

the need for external loop filter components found in

traditional PLL implementations. This is achieved by

using a digital signal processing (DSP) algorithm to

replace the loop filter commonly found in analog PLL

designs. This algorithm processes the phase detector

error term and generates a digital control value to adjust

the frequency of the voltage controlled oscillator (VCO).

This technology enables clock and data recovery with

far less jitter than is generated using traditional methods

and it eliminates performance degradation caused by

external component aging. In addition, because

external loop filter components are not required,

sensitive noise entry points are eliminated, thus making

the DSPLL less susceptible to board-level noise

sources and making SONET/SDH jitter compliance

easier to attain in the application.

Multi-Rate Operation

The Si5022/23 supports clock and data recovery for

OC-48 and STM-16 data streams. In addition, the PLL

was designed to operate at data rates up to 2.7 Gbps to

support OC-48/STM-16 applications that employ

forward error correction (FEC).

Multi-rate operation is achieved by configuring the

device to divide down the output of the VCO to the

desired data rate. The divide factor is configured by the

RATESEL[0:1] pins. The RATESEL[0:1] configuration

and associated data rates are given in Table 7.

Operation Without an External Reference

The Si5022/23 can perform clock and data recovery

without an external reference clock. Tying the REFCLK

inputs to GND configures the device to operate without

an external reference clock. Clock recovery is achieved

by monitoring the timing quality of the incoming data

relative to the VCO frequency. Lock is maintained by

continuously monitoring the incoming data timing quality

and adjusting the VCO accordingly. Details of the lock

detection and the lock-to-reference functions while in

this mode are described in their respective sections

below.

Note:

Without an external reference the acquisition of data is

dependent solely on the data itself and will typically

require more time to acquire lock than when a refer-

ence is applied.

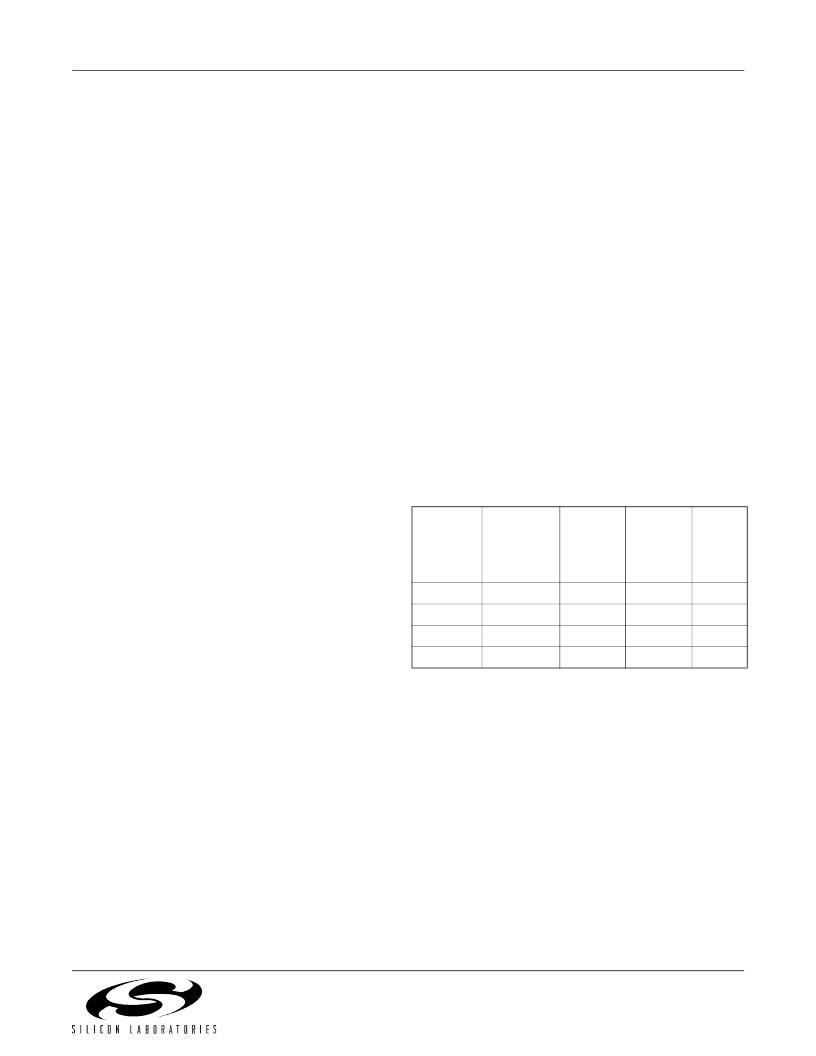

Table 7. Multi-Rate Configuration

RATESEL

[0:1]

SONET/

SDH

Gigabit

Ethernet

OC-48

with

15/14

FEC

CLK

Divider

11

2.488 Gbps

—

2.67 Gbps

1

10

1.244 Gbps

1.25 Gbps

—

2

01

622.08 Mbps

—

—

4

00

155.52 Mbps

—

—

16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SI5023 | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| Si5023-BM | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| SI5022 | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| SI5311 | PRECISION HIGH SPEED CLOCK MULTIPLIER/REGENERATOR IC |

| SI5311-BM | BAIL MOUNT/100 BULK PKG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI5022-BMR | 功能描述:時鐘合成器/抖動清除器 SNT/SDH GbE 2.7Gbps OC48/12/3 STM16/4/1 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SI5022-EVB | 功能描述:時鐘和定時器開發(fā)工具 SNT/SDH GbE 2.7Gbps OC48/12/3 STM16/4/1 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類型:Clock Conditioners 工具用于評估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| SI5023 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| SI-50230-F | 制造商:Bel Fuse 功能描述:- Trays |

| SI-50230-G | 制造商:Bel Fuse 功能描述:- Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。