- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373395 > Si5022-BM (Electronic Theatre Controls, Inc.) MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP PDF資料下載

參數(shù)資料

| 型號(hào): | Si5022-BM |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 運(yùn)動(dòng)控制電子 |

| 英文描述: | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| 中文描述: | 多速率SONET / SDH的CDR集成電路限幅放大器 |

| 文件頁(yè)數(shù): | 1/22頁(yè) |

| 文件大小: | 399K |

| 代理商: | SI5022-BM |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

Preliminary Rev. 0.46 5/01

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Silicon Laboratories Confidential. Information contained herein is covered under non-disclosure agreement (NDA).

Copyright 2001 by Silicon Laboratories

Si5022/23-DS046

Si5022/Si5023

P

RELIMINARY

D

ATA

S

HEET

M

ULTI

-R

ATE

SONET/SDH CDR IC

WITH

L

IMITING

A

MP

Features

H

igh Speed Clock and Data Recovery device with Integrated Limiting Amp:

Applications

Description

The Si5022/23 is a fully integrated, high performance limiting amp and clock and

data recovery (CDR) IC for high-speed serial communication systems. It extracts

timing information and data from a serial input at OC-48/12/3, STM-16/4/1, or

Gigabit Ethernet (GbE) rates. Support for 2.7 Gbps data streams is also provided

for OC-48/STM-16 applications that employ forward error correction (FEC). An

external reference clock is not required; applications with or without an external

reference clock are supported. Silicon Laboratories’ DSPLL

technology

eliminates sensitive noise entry points thus making the PLL less susceptible to

board-level interaction and helping to ensure optimal jitter performance.

The Si5022/23 represents a new standard in low jitter, low power, small size, and

integration for high speed LA/CDRs. It operates from either a 3.3 V (Si5023) or

2.5 V (Si5022) supply over the industrial temperature range (–40°C to 85°C).

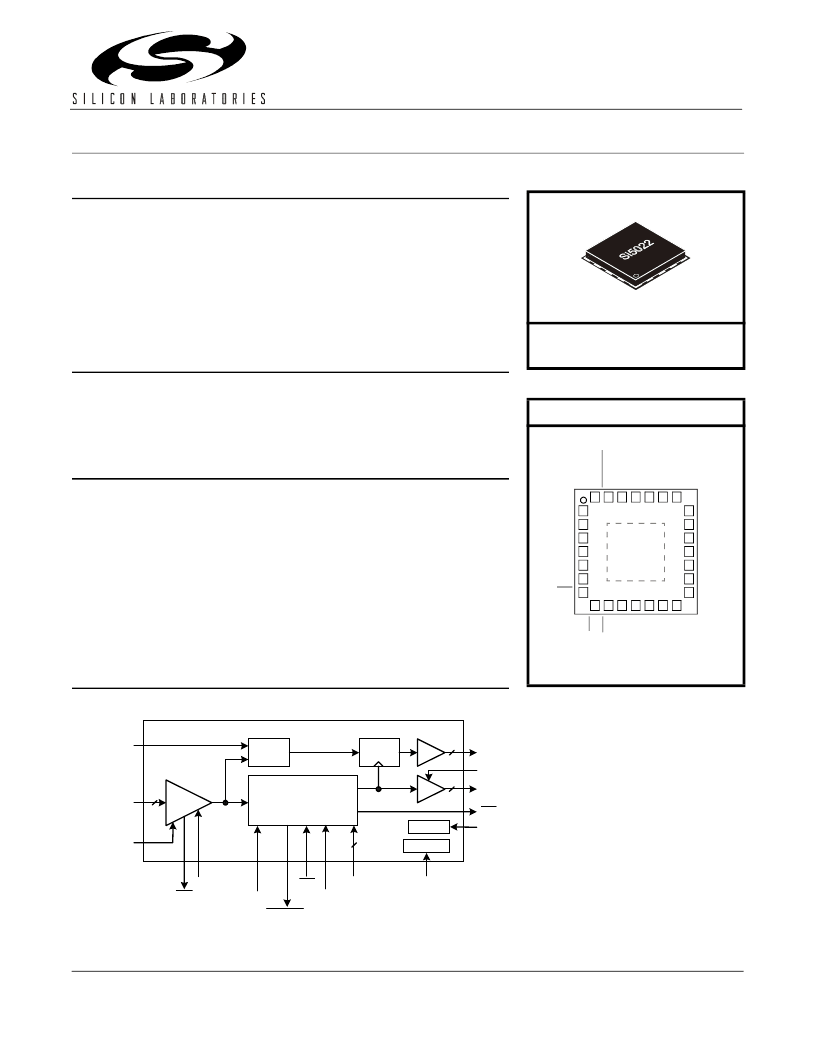

Functional Block Diagram

!

Supports OC-48/12/3, STM-16/4/1,

Gigabit Ethernet, and 2.7 Gbps FEC

!

DSPLL Technology

!

Low Power—370 mW (TYP)

!

Small Footprint: 5 mm x 5 mm

!

Bit-Error-Rate Alarm

!

External Reference Not Required

!

Jitter Generation 3.0 mUI

RMS

(TYP)

!

Loss-of-signal Level Alarm

!

Data Slicing Level Control

!

10 mV

PP

Differential Sensitivity

!

2.5 V (Si5022) or 3.3 V (Si5023) Supply

!

!

!

!

SONET/SDH/ATM Routers

Add/Drop Multiplexers

Digital Cross Connects

Gigabit Ethernet Interfaces

!

!

!

!

SONET/SDH Test Equipment

Optical Transceiver Modules

SONET/SDH Regenerators

Board Level Serial Links

Limiting

AMP

DSPLL

TM

Phase-Locked

Loop

BUF

BUF

Retimer

DIN+

DIN–

LOS_LVL

SLICE_LVL

LOS

2

2

2

LOL

CLKOUT+

CLKOUT–

DOUT+

DOUT–

CLKDSBL

Bias Gen

REXT

Squelch

Control

DSQLCH

RESET/CAL

BER_ALM

RATSEL[1:0]

2

REFCLK+

REFCLK–

(Optional)

LTR

BER_LVL

Control

Ordering Information:

See page 14.

Pin Assignments

Si5022/23

1

RATESEL0

GND

Pad

Top View

2

3

4

5

6

7

21

20

19

18

17

16

15

14

13

12

11

10

9

8

22

23

24

25

26

27

28

RATESEL1

LOS_LVL

SLICE_LVL

REFCLK+

REFCLK–

LOL

VDD

REXT

RESET/CAL

VDD

DOUT+

DOUT–

TDI

N

B

B

V

C

C

C

L

L

D

V

D

D

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SI5023 | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| Si5023-BM | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| SI5022 | MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| SI5311 | PRECISION HIGH SPEED CLOCK MULTIPLIER/REGENERATOR IC |

| SI5311-BM | BAIL MOUNT/100 BULK PKG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI5022-BMR | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 SNT/SDH GbE 2.7Gbps OC48/12/3 STM16/4/1 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SI5022-EVB | 功能描述:時(shí)鐘和定時(shí)器開(kāi)發(fā)工具 SNT/SDH GbE 2.7Gbps OC48/12/3 STM16/4/1 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類型:Clock Conditioners 工具用于評(píng)估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| SI5023 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MULTI-RATE SONET/SDH CDR IC WITH LIMITING AMP |

| SI-50230-F | 制造商:Bel Fuse 功能描述:- Trays |

| SI-50230-G | 制造商:Bel Fuse 功能描述:- Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。