- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373394 > SI3014-KS (Electronic Theatre Controls, Inc.) 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT PDF資料下載

參數(shù)資料

| 型號(hào): | SI3014-KS |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT |

| 中文描述: | 3.3伏催化裂化/ JATE直接訪問(wèn)安排 |

| 文件頁(yè)數(shù): | 23/54頁(yè) |

| 文件大?。?/td> | 1407K |

| 代理商: | SI3014-KS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

Si3035

Rev. 1.2

23

The main design consideration is the generation of a

base frequency, defined as the following:

N1 (Register 7) and M1 (Register 8) are 8-bit unsigned

values. F

MCLK

is the clock provided to the MCLK pin.

Table 18 lists several standard crystal oscillator rates

that could be supplied to MCLK. This list simply

represents a sample of MCLK frequency choices. Many

more are possible.

After the first PLL has been setup, the second PLL can

be programmed easily. The values for N2 and M2

(Register 9) are shown in Table 17. N2 and M2 are 4-bit

unsigned values.

When programming the registers of the clock generator,

the order of register writes is important. For PLL1

updates, N1 (Register 7) must always be written first,

immediately followed by a write to M1 (Register 8). For

PLL2, the CGM bit must be set as desired prior to

writing N2/M2 (Register 9). Changes to the CGM bit

only take effect when N2/M2 are written.

Note:

The values shown in Table 17 and Table 18 satisfy the

equations above. However, when programming the

registers for N1, M1, N2, and M2, the value placed in

these registers must be one less than the value calcu-

lated from the equations. For example, for CGM = 0

with a MCLK of 48.0 MHz, the values placed in the N1

and M1 registers would be 0x7C and 0x5F, respec-

tively. If CGM = 1, a non-zero value must be pro-

grammed to Register 9 in order for the 16/25 ratio to

take effect.

PLL Lock Times

The Si3035 changes sample rates very quickly.

However, lock time will vary based on the programming

of the clock generator. The major factor contributing to

PLL lock time is the CGM bit. When the CGM bit is used

(set to 1), PLL2 will lock slower than when CGM is 0.

The following relationships describe the boundaries on

PLL locking time:

PLL1 lock time < 1 ms (CGM = 0,1)

PLL2 lock time: 100 us to 1 ms (CGM = 0)

PLL2 lock time <1 ms (CGM = 1)

For modem designs, it is recommended that PLL1 be

programmed

during

initialization.

programming of PLL1 is necessary. The CGM bit and

PLL2 can be programmed for the desired initial sample

No

further

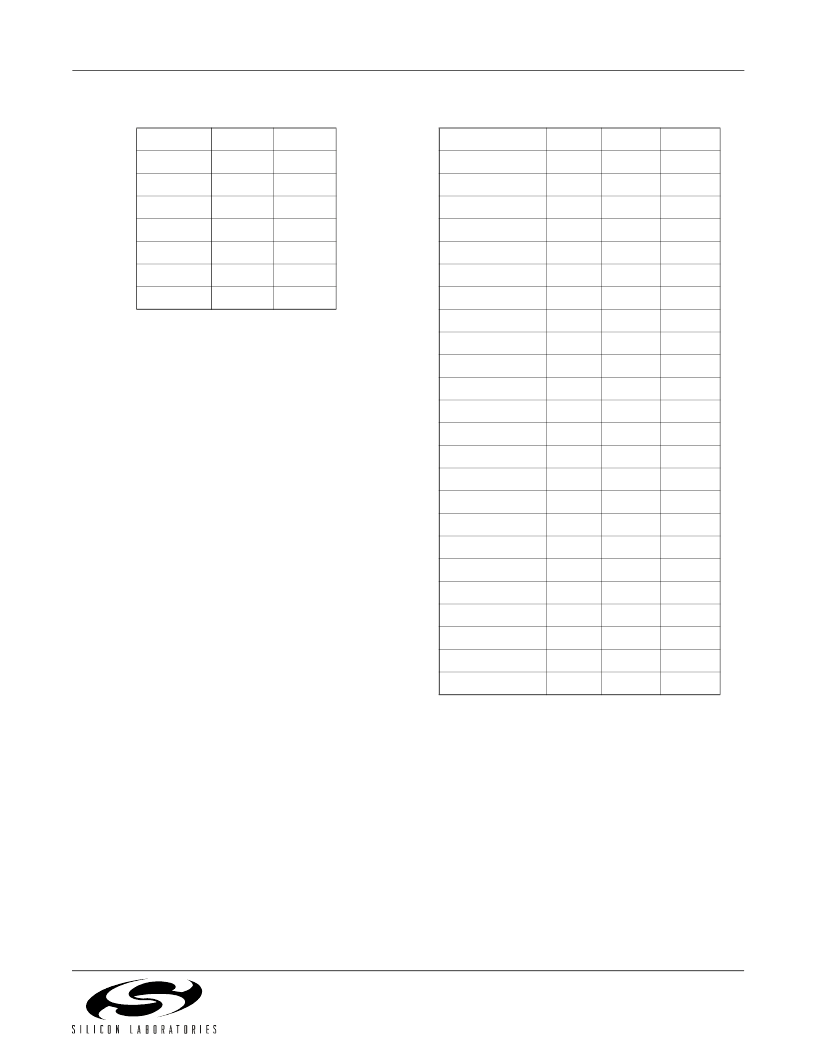

Table 17. N2, M2 Values (CGM = 0, 1)

Fs (Hz)

N2

M2

7200

2

2

8000

9

10

8229

7

8

8400

6

7

9000

4

5

9600

3

4

10286

7

10

FBase

FMCLK

M1

N1

36.864MHz CGM

,

0

=

=

=

FBase

N1 25

16

FMCLKM1

36.864MHz CGM

,

1

=

=

=

Table 18. MCLK Examples

MCLK (MHz)

N1

M1

CGM

1.8432

1

20

0

4.0000

5

72

1

4.0960

1

9

0

5.0688

11

80

0

6.0000

5

48

1

6.1440

1

6

0

8.1920

32

225

1

9.2160

1

4

0

10.0000

25

144

1

10.3680

9

32

0

11.0592

3

10

0

12.288

1

3

0

14.7456

2

5

0

16.0000

5

18

1

18.4320

1

2

0

24.5760

32

75

1

25.8048

7

10

0

33.8688

147

160

0

44.2368

96

125

1

46.0800

5

4

0

47.9232

13

10

0

48.0000

125

96

0

56.0000

35

36

1

60.0000

25

24

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SI3014-KT | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT |

| SI3015-BS | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT |

| SI3015-KS | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT |

| SI3021 | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT |

| SI3021-BS | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SI3014-KSR | 制造商:Silicon Laboratories Inc 功能描述: |

| SI3014-KT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:GLOBAL MC 97 SILICON DAA |

| SI3015 | 制造商:SILABS 制造商全稱:SILABS 功能描述:V.22BIS ISOMODEM CHIPSET WITH ERROR CORRECTION |

| SI3015-BS | 功能描述:電信線路管理 IC CONTACT SILICON LABS FOR AVAILABILITY RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| SI3015-BSR | 功能描述:電信線路管理 IC CONTACT SILICON LABS FOR AVAILABILITY RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。