- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372122 > SC28L202A1B (NXP SEMICONDUCTORS) Dual universal asynchronous receiver/transmitter DUART PDF資料下載

參數(shù)資料

| 型號: | SC28L202A1B |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Dual universal asynchronous receiver/transmitter DUART |

| 中文描述: | 2 CHANNEL(S), 3M bps, SERIAL COMM CONTROLLER, PQFP52 |

| 封裝: | 10 X 10 MM, 2 MM HEIGHT, PLASTIC, MO-108, SOT-379-1, QFP-52 |

| 文件頁數(shù): | 50/77頁 |

| 文件大?。?/td> | 531K |

| 代理商: | SC28L202A1B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

Philips Semiconductors

Objective specification

SC28L202

Dual UART

2000 Feb 10

44

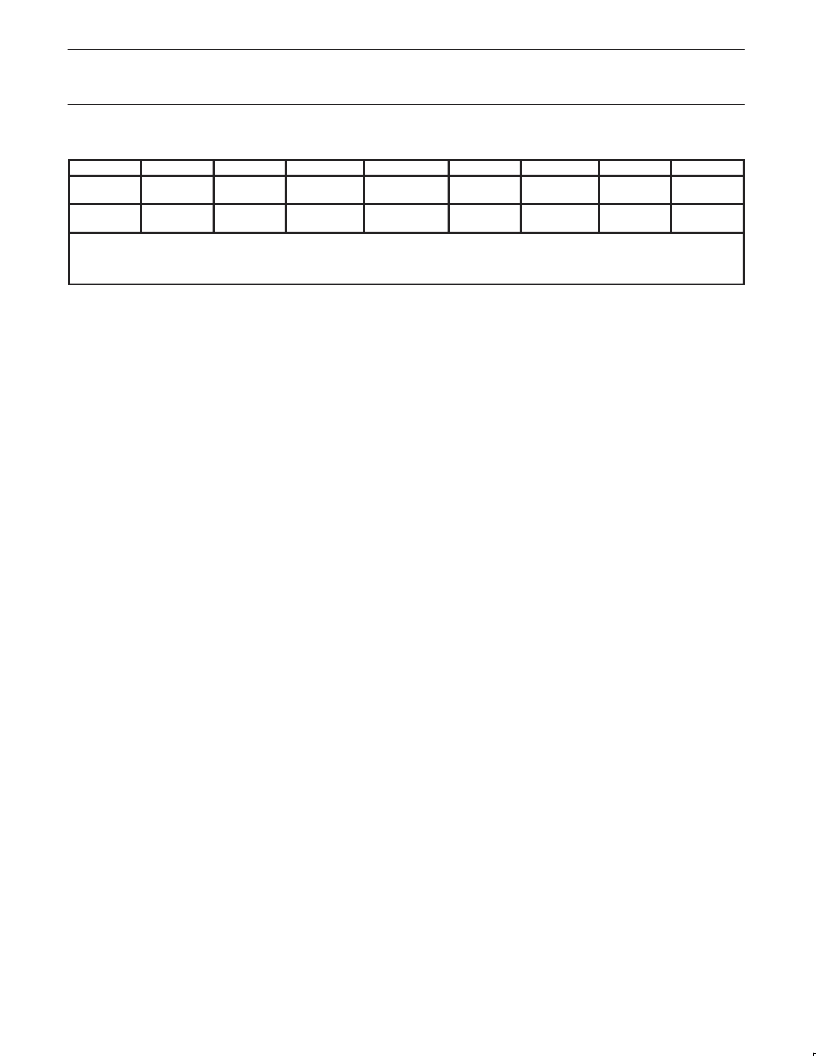

SR Status Register

Bit 7

RECEIVED

BREAK*

0 = No

1 = Yes

BIT 6

FRAMING

ERROR*

0 = No

1 = Yes

BIT 5

PARITY

ERROR*

0 = No

1 = Yes

BIT 4

OVERRUN

ERROR

0 = No

1 = Yes

BIT 3

TxEMT

BIT 2

TxRDY

BIT 1

FFULL

BIT 0

RxRDY

SR A

SR B

0 = No

1 = Yes

0 = No

1 = Yes

0 = No

1 = Yes

0 = No

1 = Yes

NOTE: *These status bits are appended to the corresponding data character in the receive FIFO. A read of the status provides these bits

(7:5) from the top of the FIFO together with bits (4:0). These bits are cleared by a “reset error status” command. In character mode they are

discarded when the corresponding data character is read from the FIFO. In block error mode, the error–reset command (command 4x or

receiver reset) must used to clear block error conditions

SR A[7] – Received Break

Channel A Received Break. This bit indicates that an all zero

character of the programmed length has been received without a

stop bit. Only a single FIFO position is occupied when a break is

received: further entries to the FIFO are inhibited until the RxD A line

returns to the marking state for at least one–half a bit time two

successive edges of the internal or external 1X clock. This will

usually require a high time of one X1 clock period or 3 X1 edges

since the clock of the controller is not synchronous to the X1 clock.

When this bit is set, the Channel A ‘change in break’ bit in the ISR

(ISR[2]) is set. ISR[2] is also set when the end of the break

condition, as defined above, is detected.

The break detect circuitry can detect breaks that originate in the

middle of a received character. However, if a break begins in the

middle of a character, it must persist until at least the end of the next

character time in order for it to be detected.

This bit is reset by command 4 (0100) written to the command

register or by receiver reset.

SR A[6] – Channel A Framing Error

This bit, when set, indicates that a stop bit was not detected when

the corresponding data character in the FIFO was received. The

stop bit check is made in the middle of the first stop bit position.

SR A[5] – Channel A Parity Error

This bit is set when the ‘with parity’ or ‘force parity’ mode is

programmed and the corresponding character in the FIFO was

received with incorrect parity.

In the special multi–drop mode the parity error bit stores the receive

A/D (Address/Data) bit.

SR A[4] – Channel A Overrun Error

This bit, when set, indicates that one or more characters in the

received data stream have been lost. It is set upon receipt of a new

character when the FIFO is full and a character is already in the

receive shift register waiting for an empty FIFO position. When this

occurs, the character in the receive shift register (and its break

detect, parity error and framing error status, if any) is lost.

This bit is cleared by a ‘reset error status’ command.

SR A[3] – Channel A Transmitter Empty (TxEMT A)

This bit will be set when the transmitter under runs, i.e., both the

TxEMT and TxRDY bits are set. This bit and TxRDY are set when

the transmitter is first enabled and at any time it is re–enabled after

either (a) reset, or (b) the transmitter has assumed the disabled

state. It is always set after transmission of the last stop bit of a

character if no character is in the THR awaiting transmission.

It is reset when the THR is loaded by the CPU, a pending

transmitter disable is executed, the transmitter is reset, or the

transmitter is disabled while in the under run condition.

SR A[2] – Channel A Transmitter Ready (TxRDY A)

This bit, when set, indicates that the transmit FIFO is not full and

ready to be loaded with another character. This bit is cleared when

the transmit FIFO is loaded by the CPU and there are (after this

load) no more empty locations in the FIFO. It is set when a

character is transferred to the transmit shift register. TxRDY A is

reset when the transmitter is disabled and is set when the

transmitter is first enabled. Characters loaded to the TxFIFO while

this bit is 0 will be lost. This bit has different meaning from ISR[0].

SR A[1] – Channel A FIFO Full (FFULL A)

This bit is set when a character is transferred from the receive shift

register to the receive FIFO and the transfer causes the FIFO to

become full, i.e., all eight FIFO positions are occupied. It is reset

when the CPU reads the receive FIFO. If a character is waiting in

the receive shift register because the FIFO is full, FFULL A will not

be reset when the CPU reads the receive FIFO. This bit has

different meaning from ISR1 when MR1 6 is programmed to a ‘1’.

SR A[0] – Channel A Receiver Ready (RxRDY A)

This bit indicates that a character has been received and is waiting

in the FIFO to be read by the CPU. It is set when the character is

transferred from the receive shift register to the FIFO and reset

when the CPU reads the receive FIFO, only if (after this read) there

are no more characters in the FIFO.

SR B – Channel B Status Register

The bit definitions for this register are identical to the bit definitions

for SR A, except that all status applies to the Channel B receiver

and transmitter and the corresponding inputs and outputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC28L202A1D | Dual universal asynchronous receiver/transmitter DUART |

| SC431CS8DE2 | Analog IC |

| SC431CS8DE3 | Analog IC |

| SC431CS8DF1 | Analog IC |

| SC431CS8DF2 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC28L202A1D | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual universal asynchronous receiver/transmitter DUART |

| SC28L202A1DGG | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS 256B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L202A1DGG,112 | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L202A1DGG,118 | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L202A1DGG,129 | 功能描述:UART 接口集成電路 3-5V 2CH UART 3MBPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。