- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372122 > SC26L198C1A (NXP SEMICONDUCTORS) Octal UART with TTL compatibility at 3.3V and 5V supply voltages PDF資料下載

參數(shù)資料

| 型號: | SC26L198C1A |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Octal UART with TTL compatibility at 3.3V and 5V supply voltages |

| 中文描述: | 8 CHANNEL(S), 500K bps, SERIAL COMM CONTROLLER, PQCC84 |

| 封裝: | PLASTIC, LCC-84 |

| 文件頁數(shù): | 27/49頁 |

| 文件大?。?/td> | 358K |

| 代理商: | SC26L198C1A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

Philips Semiconductors

Product specification

SC26C198 SC68C198

SC26L198 SC68L198

Octal UART with TTL compatibility at 3.3V

and 5V supply voltages

1995 May 1

362

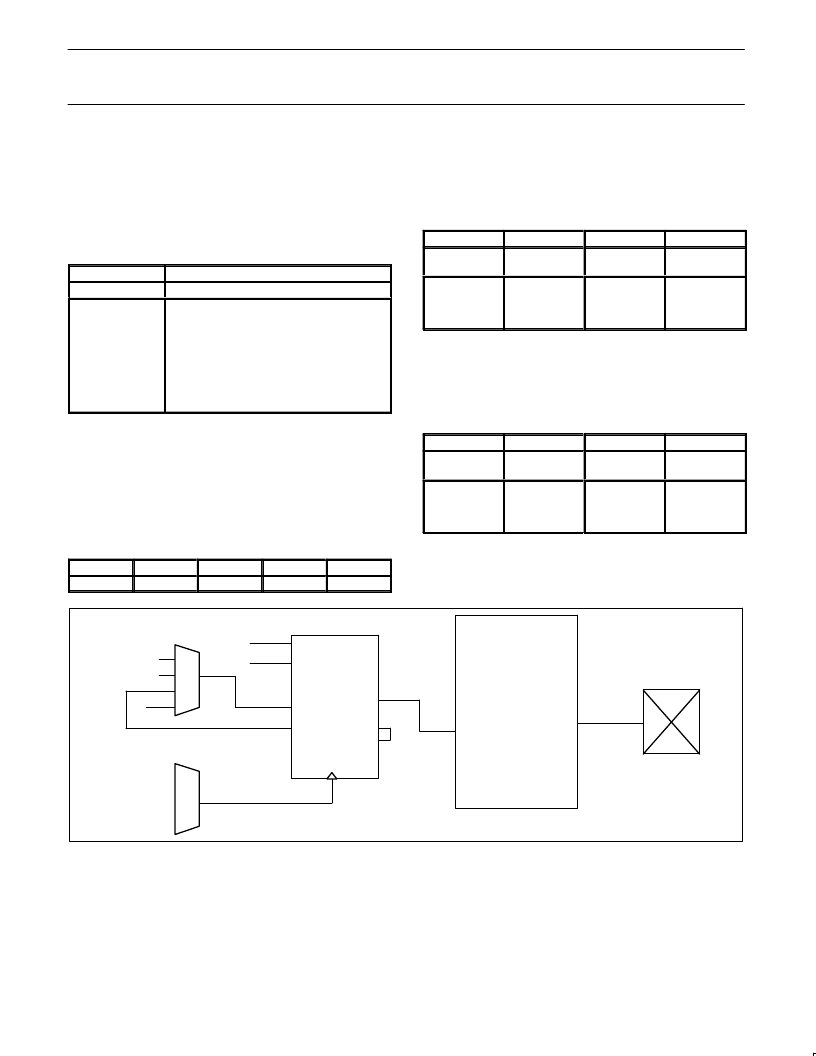

clocking mechanism that will allow the pin to change synchronously

with an internal or external stimulus. See diagram below.

Table 39. GPOSR – General Purpose Output

Select Register

GPOSR selects the signal or data source for the G

OUT

0 pin. The Tx

changes.

Bits 7:4

1000 = TxC1x a

1011 = TxC16x b

1101 = GGPOR(2)

áááááá

áááááá

áááááá

ááááááááááááááááá

áááááááááááá

áááááááááááá

Bits 3:0

áááááá

áááááááááááá

áááááááááááá

áááááá

áááááá

áááááá

áááááá

áááááá

áááááá

Register

This register is a read/write register. Its contents may be altered by

a GPOR Write or by the GPOC and GPOD registers shown below.

The GPOD and GPOC may be programmed to cause the individual

bits of the GPOR to change synchronously with internal or external

events. The cells of this register may be thought of as a “Two Port

flip-flop”; one port is controlled by a D input and clock, the other by a

Bits 7:4

Bit 3

Bit 2

Reserved

GPOR(3)

GPOR(2)

áááááááááááá

áááááááááááá

áááááááááááá

áááááááááááá

áááááááááááá

áááááááááááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

áááá

Bit 1

áááá

GPOR(1)

áááá

ááááá

ááááá

Bit 0

ááááá

GPOR(0)

ááááá

Table 41. GPOC – General Purpose Output Clk

Register

This controls the clock source for GPOR that will clock and/or toggle

the data from the selected GPOD source. When code b’00 is

Bits 7:6

Bits 5:4

Clk Sel

01 = G

IN

0

11 = reserved

11 = reserved

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

Clk Sel

ááááá

ááááá

ááááá

Bits 3:2

Clk Sel

01 = G

IN

0

11 = I/O3c

ááááá

ááááá

ááááá

Bits 1:0

Clk Sel

01 = G

IN

0

11 = I/O3a

ááááá

ááááááááááááááááá

01 = G

IN

0

ááááá

ááááá

ááááá

Register

This register selects the data that will be presented to the GPOR “D”

input. Note that selection b’10 selects the inverted GPOR data as

Bits 7:6

Bits 5:4

Data Sel

01 = ’0’

11 = reserved

11 = reserved

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

Data Sel

ááááá

Bits 3:2

Data Sel

01 = ’0’

11 = I/O3d

ááááá

ááááá

Bits 1:0

Data Sel

01 = ’0’

11 = I/O3b

ááááá

ááááá

ááááá

ááááá

ááááá

01 = ’0’

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

ááááá

4:1 MULTIPLEX

“1”

“0”

NONE

1/O3a

D CLOCK

QN

D INPUT

DATA READ/WRITE

DATA IN/OUT

GPORON

DATA BUS

GPOR R/W

GPOR

GPOD

GPOSR

1/O3b

G

IN

0

G

IN

1

4:1 MULTIPLEX

GPO PIN

8:1 MULTIPLEX

TxC1Xa

TxC16Xa

RxC16Xa

TxC16Xb

GPOR(0)

GPOR(1)

GPOR(2)

GPOR(3)

SD00526

Figure 1. General Purpose Pin Control Logic

相關PDF資料 |

PDF描述 |

|---|---|

| SC26C198 | Octal UART with TTL compatibility at 3.3V and 5V supply voltages |

| SC26C198A1A | Octal UART with TTL compatibility at 3.3V and 5V supply voltages |

| SC26C198C1A | Octal UART with TTL compatibility at 3.3V and 5V supply voltages |

| SC68C198 | Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 50 psi, Absolute, Cell with body o-ring, 10 Vdc excitation |

| SC68C198A1A | Octal UART with TTL compatibility at 3.3V and 5V supply voltages |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SC2712A | 制造商:SPREADTRUM 功能描述:217;EWLB;6.9*8.1040;BB;TD |

| SC2712E | 制造商:SPREADTRUM 功能描述:217;EWLB;6.9X8.1;040;BB;EDGE |

| SC2738 | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:Ultra Low Output Voltage Dual Linear FET Controller |

| SC2738IMS.TRT | 制造商:Semtech Corporation 功能描述: |

| SC2738IMSTRT | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:Ultra Low Output Voltage Dual Linear FET Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。