- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379352 > SC16C754BIA68 (NXP Semiconductors N.V.) 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 64-byte FIFOs PDF資料下載

參數(shù)資料

| 型號: | SC16C754BIA68 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 收發(fā)器 |

| 英文描述: | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 64-byte FIFOs |

| 封裝: | SC16C754BIA68<SOT188-2 (PLCC68)|<<http://www.nxp.com/packages/SOT188-2.html<1<Always Pb-free,;SC16C754BIA68<SOT188-2 (PLCC68)|<<http://www.nxp.com/packages/SOT188-2.html& |

| 文件頁數(shù): | 31/51頁 |

| 文件大?。?/td> | 253K |

| 代理商: | SC16C754BIA68 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

SC16C754B_4

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 04 — 6 October 2008

31 of 51

NXP Semiconductors

SC16C754B

5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.) with 64-byte FIFOs

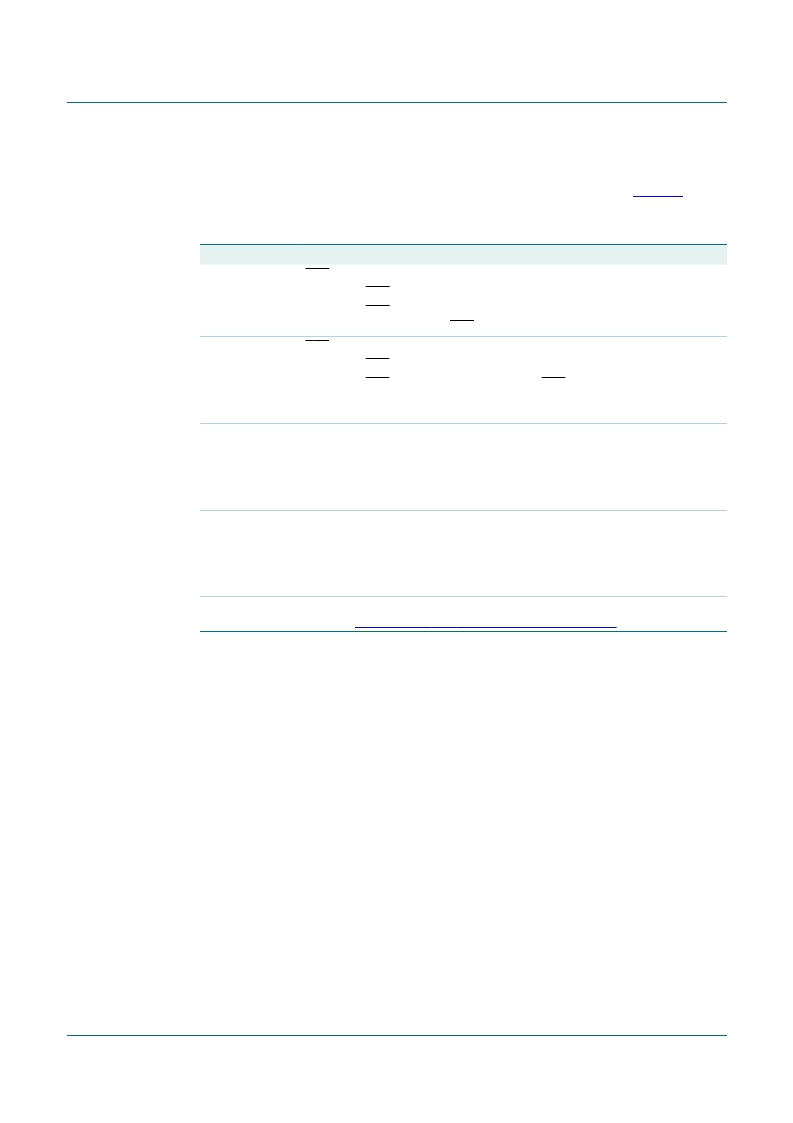

7.10 Enhanced Feature Register (EFR)

This 8-bit register enables or disables the enhanced features of the UART.

Table 19

shows

the enhanced feature register bit settings.

7.11 Divisor latches (DLL, DLM)

These are two 8-bit registers which store the 16-bit divisor for generation of the baud clock

in the baud rate generator. DLM stores the most significant part of the divisor. DLL stores

the least significant part of the divisor.

Note that DLL and DLM can only be written to before Sleep mode is enabled, that is,

before IER[4] is set.

Table 19.

Bit

7

Enhanced feature register bits description

Symbol

Description

EFR[7]

CTS flow control enable.

logic 0 = CTS flow control is disabled (normal default condition)

logic 1 = CTS flow control is enabled. Transmission will stop when a HIGH

signal is detected on the CTS pin.

EFR[6]

RTS flow control enable.

logic 0 = RTS flow control is disabled (normal default condition)

logic 1 = RTS flow control is enabled. The RTS pin goes HIGH when the

receiver FIFO HALT trigger level TCR[3:0] is reached, and goes LOW when

the receiver FIFO RESUME transmission trigger level TCR[7:4] is reached.

EFR[5]

Special character detect.

logic 0 = special character detect disabled (normal default condition)

logic 1 = special character detect enabled. Received data is compared with

Xoff2 data. If a match occurs, the received data is transferred to FIFO and

IIR[4] is set to a logic 1 to indicate a special character has been detected.

EFR[4]

Enhanced functions enable bit.

logic 0 = disables enhanced functions and writing to IER[7:4], FCR[5:4],

MCR[7:5].

logic 1 = enables the enhanced function IER[7:4], FCR[5:4], and MCR[7:5]

can be modified, that is, this bit is therefore a write enable.

EFR[3:0]

Combinations of software flow control can be selected by programming these

bits. See

Table 3 “Software flow control options (EFR[3:0])”

.

6

5

4

3:0

相關PDF資料 |

PDF描述 |

|---|---|

| SC16C754BIB80 | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 64-byte FIFOs |

| SC16C754BIBM | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 64-byte FIFOs |

| SC16C850IBS | 2.5 V to 3.3 V UART, 5 Mbit-s (max.) with 128-byte FIFOs, infrared (IrDA), and 16 mode or 68 mode parallel bus interface |

| SC16C850IET | 2.5 V to 3.3 V UART, 5 Mbit-s (max.) with 128-byte FIFOs, infrared (IrDA), and 16 mode or 68 mode parallel bus interface |

| SC16C850LIB | 1.8 V single UART, 5 Mbit-s (max.) with 128-byte FIFOs, infrared (IrDA) and 16 mode or 68 mode parallel bus interface |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SC16C754BIA68,512 | 功能描述:UART 接口集成電路 16CB 2.5V-5V 4CH RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C754BIA68,518 | 功能描述:UART 接口集成電路 4CH. UART 64B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C754BIA68,529 | 功能描述:UART 接口集成電路 16CB 2.5V-5V 4CH RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C754BIA68512 | 制造商:NXP Semiconductors 功能描述:IC QUAD UART FIFO 5MBPS 5.5V LCC-68 |

| SC16C754BIA68-S | 功能描述:UART 接口集成電路 16CB 2.5V-5V 4CH UART 64B FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。