- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372113 > SAA7130 (NXP Semiconductors N.V.) PCI video broadcast decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7130 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | PCI video broadcast decoder |

| 中文描述: | PCI視頻廣播解碼器 |

| 文件頁(yè)數(shù): | 40/48頁(yè) |

| 文件大小: | 196K |

| 代理商: | SAA7130 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

2002 Apr 23

40

Philips Semiconductors

Product specification

PCI video broadcast decoder

SAA7130HL

Notes

1.

2.

Input leakage currents include high-impedance output leakage for all bidirectional buffers with 3-state outputs.

Pins without pull-up resistors must have a 3 mA output current. Pins requiring pull-up resistors must have 6 mA;

these are pins FRAME#, TRDY#, IRDY#, DEVSEL#, SERR#, PERR#, INT_A and STOP#.

This parameter is to be interpreted as the cumulative edge rate across the specified range, rather than the

instantaneous rate at any point within the transition range.

REQ# and GNT# are point-to-point signals and have different output valid delay and input set-up times than bused

signals. GNT# has a set-up time of 10 ns. REQ# has a set-up time of 12 ns.

For purposes of active or float timing measurements, the high-impedance or ‘off’ state is defined to be when the total

current delivered through the device is less than or equal to the leakage current specification.

RST is asserted and de-asserted asynchronously with respect to CLK.

All output drivers floated asynchronously when RST is active.

V

DD(I2C)

is the extended pull-up voltage of the I

2

C-bus (3.3 or 5 V bus).

Nominal analog video input signal is to be terminated by 75

that results in 1 V (p-p) amplitude. This termination

resistor should be split into 18

and 56

, and the dividing tap should feed the video input pin, via a coupling

capacitor of 47 nF, to achieve a control range from

3 dB (attenuation) to +6 dB (amplification) for the internal

automatic gain control. See also application notes SAA7130HL/34HL.

10. See the user manuals of the SAA7130HL/34HL for Anti-Alias Filter (AAF).

11. Definition of levels and level setting:

a) The full-scale level for analog audio signals V

FS

= 0.8 V (RMS). The nominal level at the digital crossbar switch

is defined at

15 dB (FS).

b) Nominal audio input levels: external, mono, V

i

= 280 mV (RMS);

9 dB (FS).

12. The analog audio inputs (pins LEFT1, RIGHT1, LEFT2 and RIGHT2) are supported by two input levels: 1 V (RMS)

and 2 V (RMS), selectable via register setting VSEL0 (LEFT1, RIGHT1) and VSEL1 (LEFT2, RIGHT2).

3.

4.

5.

6.

7.

8.

9.

13. The definition of the duty factor:

14. The output timing must be measured with the load of a 30 pF capacitor to ground and a 500

resistor to 1.4 V.

D

ATA AND CONTROL INPUT SIGNALS ON

TS-P

PORT

(

WITH RESPECT TO SIGNAL

TS_CLK)

ON PINS

GPIO0

TO

GPIO7,

GPIO16, GPIO19

AND

GPIO22 (see Fig.19)

t

su(D)

t

h(D)

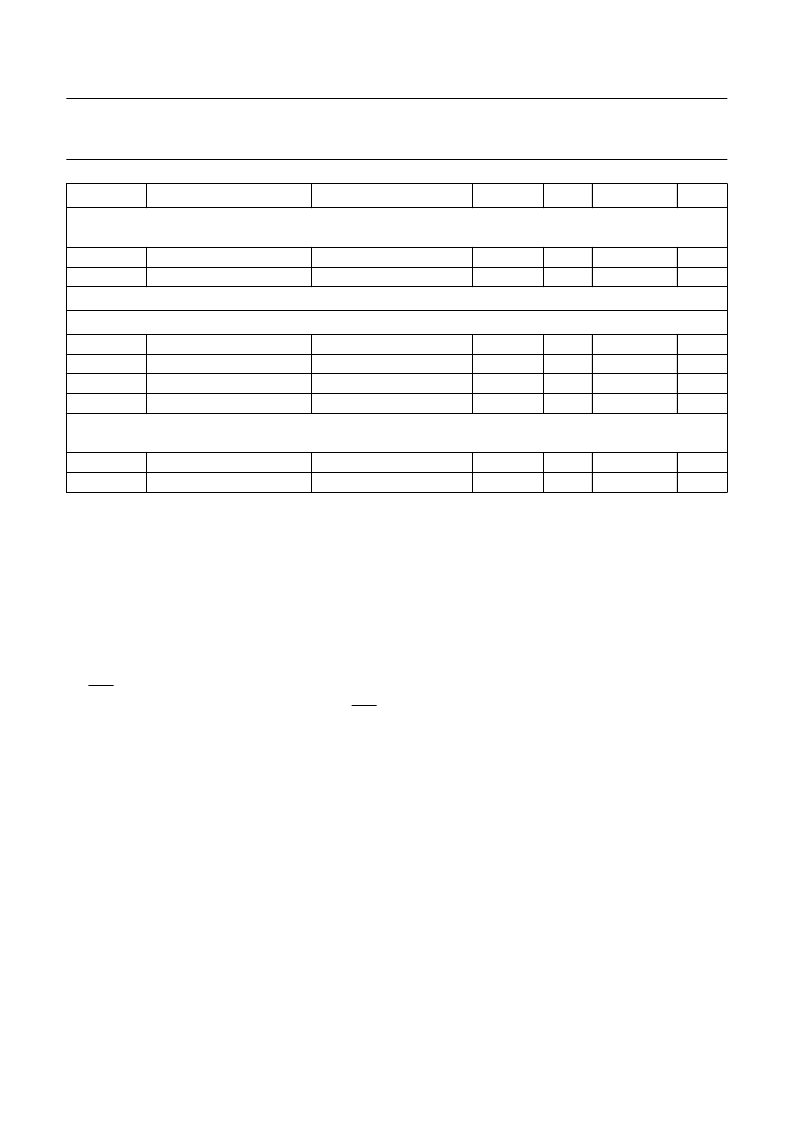

TS capture inputs with serial transport streaming (TS-S); e.g. DVB applications

input data set-up time

input data hold time

2

5

ns

ns

C

LOCK INPUT SIGNAL

TS_CLK

ON PIN

GPIO20 (see Fig.19)

T

cy

δ

t

r

t

f

D

ATA AND CONTROL INPUT SIGNALS ON

TS-S

PORT

(

WITH RESPECT TO SIGNAL

TS_CLK)

ON PINS

GPIO16, GPIO19,

GPIO21

AND

GPIO22 (see Fig.19)

cycle time

duty factor

rise time

fall time

37

40

60

5

5

ns

%

ns

ns

note 13

0.8 to 2.0 V

2.0 to 0.8 V

t

su(D)

t

h(D)

input data set-up time

input data hold time

2

5

ns

ns

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

δ

t

cy

T

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7134 | PCI audio and video broadcast decoder |

| SAA7135 | Single-chip, analog TV video/stereo DECODER |

| SAA7139 | The Digital Video Decoder/Encoder Modules(數(shù)字視頻譯碼器/編碼器模塊) |

| SAA7138 | The Digital Video Decoder/Encoder Modules(數(shù)字視頻譯碼器/編碼器模塊) |

| SAA7140A | High Performance Scaler HPS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7130HL | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:PCI video broadcast decoder |

| SAA7130HL/V1,518 | 功能描述:視頻 IC PCI 9-BIT VID DECODR RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7130HL/V1,557 | 功能描述:視頻 IC PCI 9-BIT VID DECODR RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7130HLBE | 功能描述:視頻 IC PCI 9-BIT VID DECODR RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7130HLBE-T | 功能描述:視頻 IC PCI 9-BIT VID DECODR RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。