- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372109 > SAA4952WP (NXP SEMICONDUCTORS) Memory controller PDF資料下載

參數(shù)資料

| 型號: | SAA4952WP |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Memory controller |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC44 |

| 封裝: | PLASTIC, SOT-187, LCC-44 |

| 文件頁數(shù): | 7/32頁 |

| 文件大小: | 159K |

| 代理商: | SAA4952WP |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

1997 Jun 10

7

Philips Semiconductors

Objective specification

Memory controller

SAA4952WP

By changing the active MPIP in a sequence all PIPs are

sequentially updated.

The second Multi-PIP option needs an extra PIP module.

This module produces a PIP picture which is originally

displayed at the bottom right position of the screen.

The information of the PIP picture is stored at a desired

position in the field memories. Depending on the

compression mode of the PIP module, the MPIP display

can be configured via software control

(e.g. 4

×

3, 4

×

4, etc.).

For basic features and PALplus systems a 50 Hz/1f

H

single clock mode is provided. Switching between a 2f

H

and the 1f

H

mode is performed by the SAA4952WP

hardware pin SHF to avoid wrong HDFL frequencies

which might occur in the event of a software controlled

selection. For the same reason the deflection processor is

selected via pin SDP, whereas in the case of the TDA9152

or another deflection processor without the need of a

constant 27 MHz clock, only two PLLs are necessary.

ICs from the new IC generation such as PALplus,

LIMERIC and PAN-IC need to be supplied with two clocks.

The frequency of one clock equals the frequency of the

output data (13.5, 16 or 18 MHz). A second clock operates

with twice the frequency (27, 32 or 36 MHz).

The SAA4952WP generates the necessary signals,

whereas SWC05 is obtained by dividing LLA by a factor of

two.

The display section can be set into a fixed mode via the

microcontroller port. This allows a generator mode

function for displaying OSD without a stable input signal.

A still picture can be shown on the screen completely

decoupled from the input of the converter. The generator

mode can also be used if the MPIP function is activated.

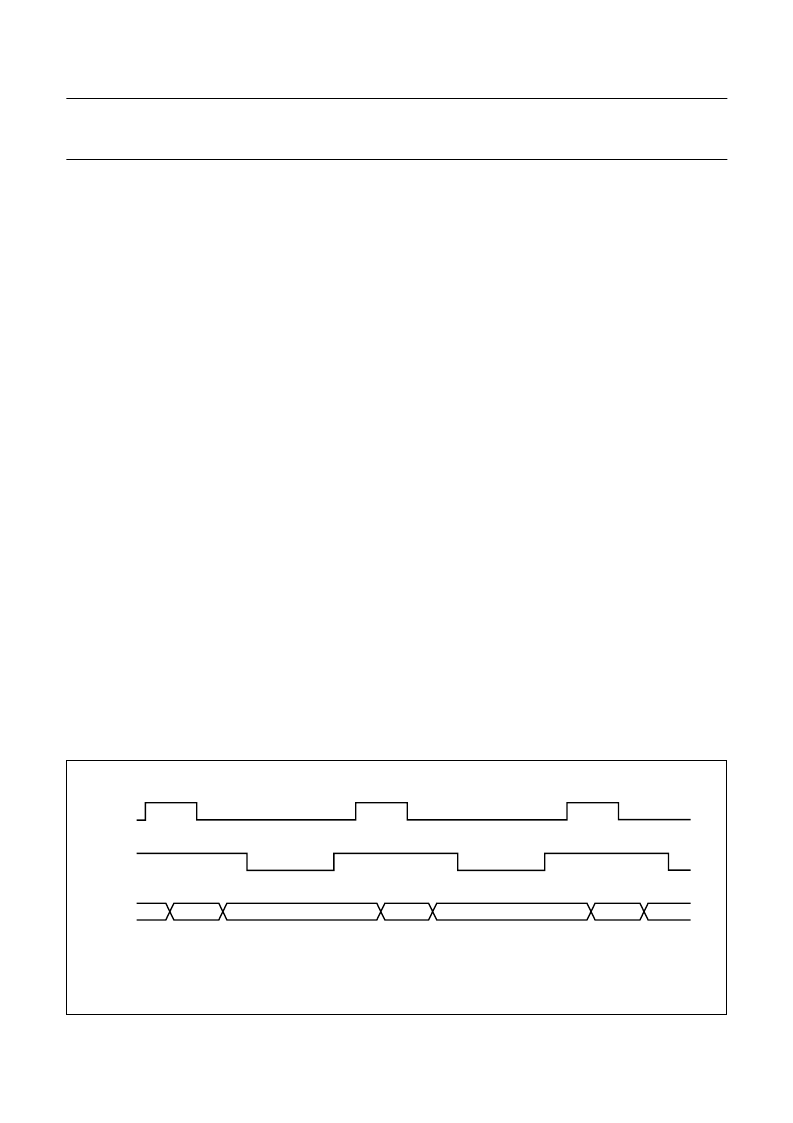

Microcontroller interface

The SAA4952WP is connected to a microcontroller via

pins P0 to P7, ALE and WRD. This controller receives

commands from the I

2

C-bus and sets the register of the

SAA4952WP accordingly. Figure 3 shows the timing of

these signals. Address and data are transmitted

sequentially on the bus with the falling edge of ALE

denoting a valid address and the falling edge of WRD

denoting valid data. The individual registers, their address

and their function are listed in Tables 1 to 12. Various

START and STOP registers are 9 bits wide, in this

instance the MSB is combined with MSBs of other signals

or fine delay control bits in an extra control register which

has to be addressed and loaded separately.

In order to load the proper values to the vertical control

registers (VWE2, VRE1 and VRE2) in the event of e.g.

median filtering, information about the current 100 Hz field

is necessary. To obtain this data, the microcontroller

sends the address 80H (read mode) which puts the

SAA4952WP in output mode for the next address/data

cycle. For this one cycle the WRD pin works as a RDN pin.

The microcontroller is able to read the length of the

incoming fields. The length is measured in multiples of

32

μ

s. The result of the measurement is a 10-bit data

word. The first 8 bits can be accessed under read address

81H. Register 80H contains the MSB and the 9th bit.

The exact knowledge of the field length makes it possible

to decide in which standard the input signal was

transmitted. The microcontroller is able to detect

non-standard sources such as a VCR in trick modes. It is

also possible to decide whether the input is interlaced or

non-interlaced. The vertical control signals to the

memories are adapted to the source to obtain a stable

display.

Fig.3 Microcontroller interface timing.

handbook, full pagewidth

MGH133

WRD

DATA

ADDRESS

ADDRESS

ADDRESS

DATA

DATA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA4955 | 2.9-Mbit field memory |

| SAA4955TJ | 2.9-Mbit field memory |

| SAA4956TJ | 2.9-Mbit field memory with noise reduction |

| SAA4960 | Integrated PAL comb filter |

| SAA4963 | Integrated NTSC comb filter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA4955 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.9-Mbit field memory |

| SAA4955TJ | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.9-Mbit field memory |

| SAA4956TJ | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:2.9-Mbit field memory with noise reduction |

| SAA4960 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated PAL comb filter |

| SAA4963 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Integrated NTSC comb filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。