- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372107 > SA7026 (NXP Semiconductors N.V.) 1.3GHz low voltage fractional-N dual frequency synthesizer PDF資料下載

參數(shù)資料

| 型號: | SA7026 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 1.3GHz low voltage fractional-N dual frequency synthesizer |

| 中文描述: | 1.3GHz的低電壓小數(shù)N頻率合成器雙 |

| 文件頁數(shù): | 7/18頁 |

| 文件大?。?/td> | 299K |

| 代理商: | SA7026 |

Philips Semiconductors

Product specification

SA7026

1.3GHz low voltage fractional-N dual synthesizer

1999 Nov 04

7

FUNCTIONAL DESCRIPTION

Main Fractional-N divider

The RFin inputs drive a pre-amplifier to provide the clock to the first

divider stage. For single ended operation, the signal should be fed to

one of the inputs while the other one is AC grounded. The

pre-amplifier has a high input impedance, dominated by pin and pad

capacitance. The circuit operates with signal levels from –18 dBm to

0 dBm, and at frequencies as high as 1.3 GHz. The divider consists

of a fully programmable bipolar prescaler followed by a CMOS

counter. Total divide ratios range from 512 to 65536.

At the completion of a main divider cycle, a main divider output

pulse is generated which will drive the main phase comparator. Also,

the fractional accumulator is incremented by the value of NF. The

accumulator works with modulo Q set by FMOD. When the

accumulator overflows, the overall division ratio N will be increased

by 1 to N + 1, the average division ratio over Q main divider cycles

(either 5 or 8) will be

Nfrac

N

NF

Q

The output of the main divider will be modulated with a fractional

phase ripple. The phase ripple is proportional to the contents of the

fractional accumulator and is nulled by the fractional compensation

charge pump.

The reloading of a new main divider ratio is synchronized to the

state of the main divider to avoid introducing a phase disturbance.

Auxiliary divider

The AUXin input drives a pre-amplifier to provide the clock to the

first divider stage. The pre-amplifier has a high input impedance,

dominated by pin and pad capacitance. The circuit operates with

signal levels from –18dBm to 0 dBm (80 to 636 mVpp), and at

frequencies as high as 550 MHz. The divider consists of a fully

programmable bipolar prescaler followed by a CMOS counter. Total

divide ratios ranges from 128 to 16383.

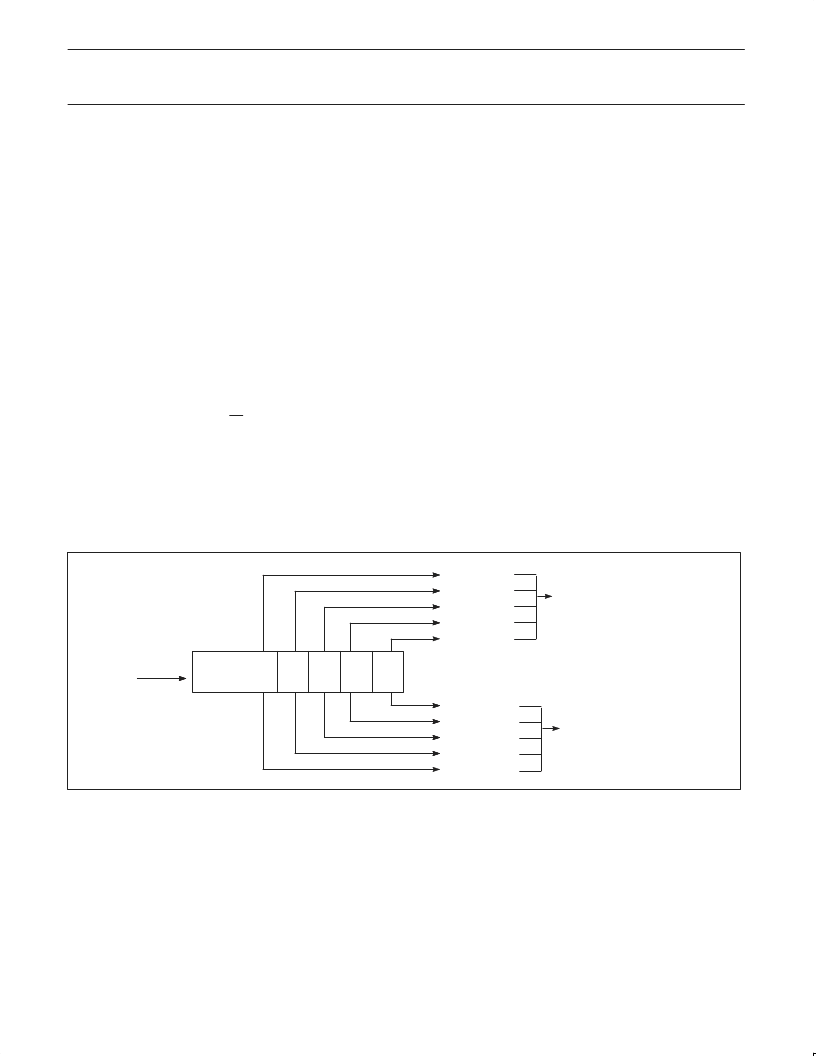

Reference divider

The reference divider consists of a divider with programmable

values between 4 and 1023 followed by a three bit binary counter.

The 3 bit SM (SA) register (see figure 4) determines which of the 5

output pulses are selected as the main (auxiliary) phase detector

input.

Phase detector (see Figure 5)

The reference and main (aux) divider outputs are connected to a

phase/frequency detector that controls the charge pump. The pump

current is set by an external resistor in conjunction with control bits

CP0 and CP1 in the C-word (see Charge Pump table). The dead

zone (caused by finite time taken to switch the current sources on or

off) is cancelled by forcing the pumps ON for a minimum time at

every cycle (backlash time) providing improved linearity.

SR01415

DIVIDE BY R

/2

/2

/2

/2

REFERENCE

INPUT

SM=”000”

SM=”001”

SM=”010”

SM=”011”

SM=”100”

SA=”100”

SA=”011”

SA=”010”

SA=”001”

SA=”000”

TO

MAIN

PHASE

DETECTOR

TO

AUXILIARY

PHASE

DETECTOR

Figure 4.

Reference Divider

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SA7026DH | 1.3GHz low voltage fractional-N dual frequency synthesizer |

| SA702 | Divide by: 64/65/72 triple modulus low power ECL prescaler |

| SA702D | Divide by: 64/65/72 triple modulus low power ECL prescaler |

| SA702N | Divide by: 64/65/72 triple modulus low power ECL prescaler |

| SA702 | SILICON GATE ENHANCEMENT MODE RF POWER VDMOS TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SA7026DH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.3GHz low voltage fractional-N dual frequency synthesizer |

| SA702D | 制造商:NXP Semiconductors 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| SA702N | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Divide by: 64/65/72 triple modulus low power ECL prescaler |

| SA703 | 制造商:Datak Corporation 功能描述:Precision ScrewDriver Set |

| SA-7030A | 功能描述:BCD 10-POSITION SMD J-HOOK RoHS:是 類別:開關(guān) >> DIP 系列:SA-7000 特色產(chǎn)品:RDM Series Rotary DIP Switch 標(biāo)準(zhǔn)包裝:70 系列:RDM 電路:十六進制 位置數(shù):16 觸點額定電壓:0.1A @ 42VDC 觸動器類型:用于工具旋轉(zhuǎn) 觸動器電平:凹槽式 安裝類型:通孔 方向:頂部觸動 可清洗:是 其它名稱:EG4977-5RDMAR16PIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。