- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299790 > PSD854F2A-90UT (STMICROELECTRONICS) 256K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | PSD854F2A-90UT |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 256K X 8 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP64 |

| 封裝: | ROHS COMPLIANT, TQFP-64 |

| 文件頁數(shù): | 13/128頁 |

| 文件大?。?/td> | 1045K |

| 代理商: | PSD854F2A-90UT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

PSD8XXFX

Summary description

Doc ID 7833 Rev 7

1

Summary description

The PSD8XXFX family of memory systems for microcontrollers (MCUs) brings in-system-

programmability (ISP) to Flash memory and programmable logic. The result is a simple and

flexible solution for embedded designs. PSD devices combine many of the peripheral

functions found in MCU based applications.

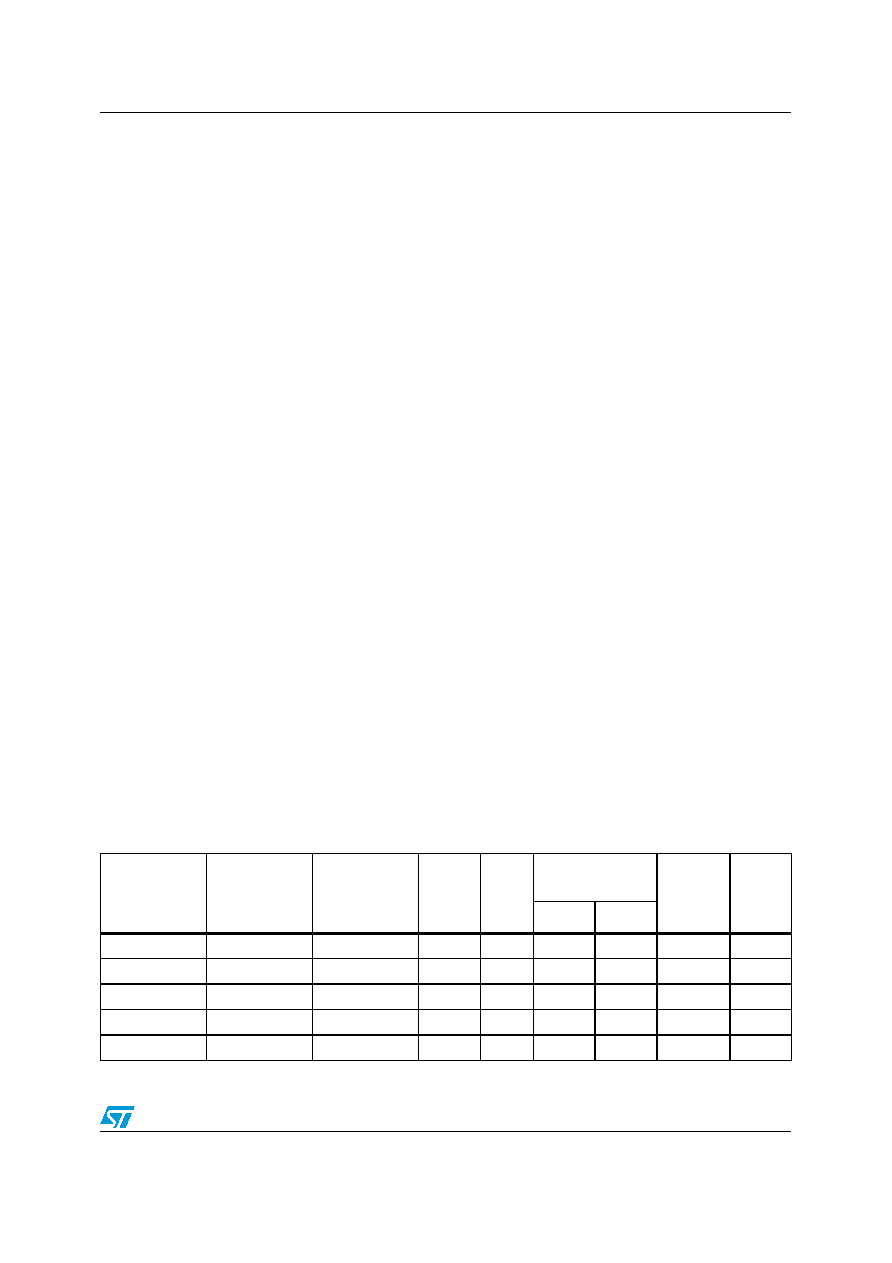

Table 2 summarizes all the devices.

The CPLD in the PSD devices features an optimized macrocell logic architecture. The PSD

macrocell was created to address the unique requirements of embedded system designs. It

allows direct connection between the system address/data bus, and the internal PSD

registers, to simplify communication between the MCU and other supporting devices.

The PSD device includes a JTAG serial programming interface, to allow in-system

programming (ISP) of the entire device. This feature reduces development time, simplifies

the manufacturing flow, and dramatically lowers the cost of field upgrades. Using ST’s

special Fast-JTAG programming, a design can be rapidly programmed into the PSD in as

little as seven seconds.

The innovative PSD8XXFX family solves key problems faced by designers when managing

discrete Flash memory devices, such as:

●

First-time in-system programming (ISP)

●

Complex address decoding

●

Simultaneous read and write to the device.

The JTAG Serial Interface block allows in-system programming (ISP), and eliminates the

need for an external Boot EPROM, or an external programmer. To simplify Flash memory

updates, program execution is performed from a secondary Flash memory while the primary

Flash memory is being updated. This solution avoids the complicated hardware and

software overhead necessary to implement IAP.

ST makes available a software development tool, PSDsoft Express, that generates ANSI-

C compliant code for use with your target MCU. This code allows you to manipulate the non-

volatile memory (NVM) within the PSD. Code examples are also provided for:

●

Flash memory IAP via the UART of the host MCU

●

Memory paging to execute code across several PSD memory pages

●

Loading, reading, and manipulation of PSD macrocells by the MCU.

Table 2.

Product range

Part number(1)

Primary Flash

memory

(8 sectors)

Secondary

Flash memory

(4 sectors)

SRAM

I/O

ports

Number of

macrocells

Serial ISP

JTAG/ISC

port

Turbo

mode

Input

Output

PSD813F2

1 Mbit

256 Kbit

16 Kbit

27

24

16

yes

PSD813F4

1 Mbit

256 Kbit

none

27

24

16

yes

PSD813F5

1 Mbit

none

27

24

16

yes

PSD833F2

1 Mbit

256 Kbit

64 Kbit

27

24

16

yes

PSD834F2

2 Mbit

256 Kbit

64 Kbit

27

24

16

yes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PSH665-FREQ-OUT1 | VCXO, SINE OUTPUT, 465 MHz - 865 MHz |

| PSM3-022K | 1 ELEMENT, 0.022 uH, GENERAL PURPOSE INDUCTOR, SMD |

| PSM3-068K | 1 ELEMENT, 0.068 uH, GENERAL PURPOSE INDUCTOR, SMD |

| PSM3-120K | 1 ELEMENT, 0.12 uH, GENERAL PURPOSE INDUCTOR, SMD |

| PSM3-121K | 1 ELEMENT, 1.2 uH, GENERAL PURPOSE INDUCTOR, SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PSD854F2V-12JI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 3.0V 2M 120ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2V-12MI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 3.0V 2M 120ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2V-90J | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 3.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD854F2V-90M | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 3.0V 2M 90ns RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| PSD-8M-01 | 制造商:Richco 功能描述:CB SPT REST MNT NAT 8MM SPC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。