- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368096 > PPC440GX-3CC533S (APPLIEDMICRO INC) Power PC 440GX Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | PPC440GX-3CC533S |

| 廠商: | APPLIEDMICRO INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Power PC 440GX Embedded Processor |

| 中文描述: | 32-BIT, 533 MHz, RISC PROCESSOR, CBGA552 |

| 封裝: | 25 X 25 MM, CERAMIC, FBGA-552 |

| 文件頁(yè)數(shù): | 53/93頁(yè) |

| 文件大?。?/td> | 794K |

| 代理商: | PPC440GX-3CC533S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)當(dāng)前第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)

440GX – Power PC 440GX Embedded Processor

AMCC

53

Revision 1.15 – August 30, 2007

Data Sheet

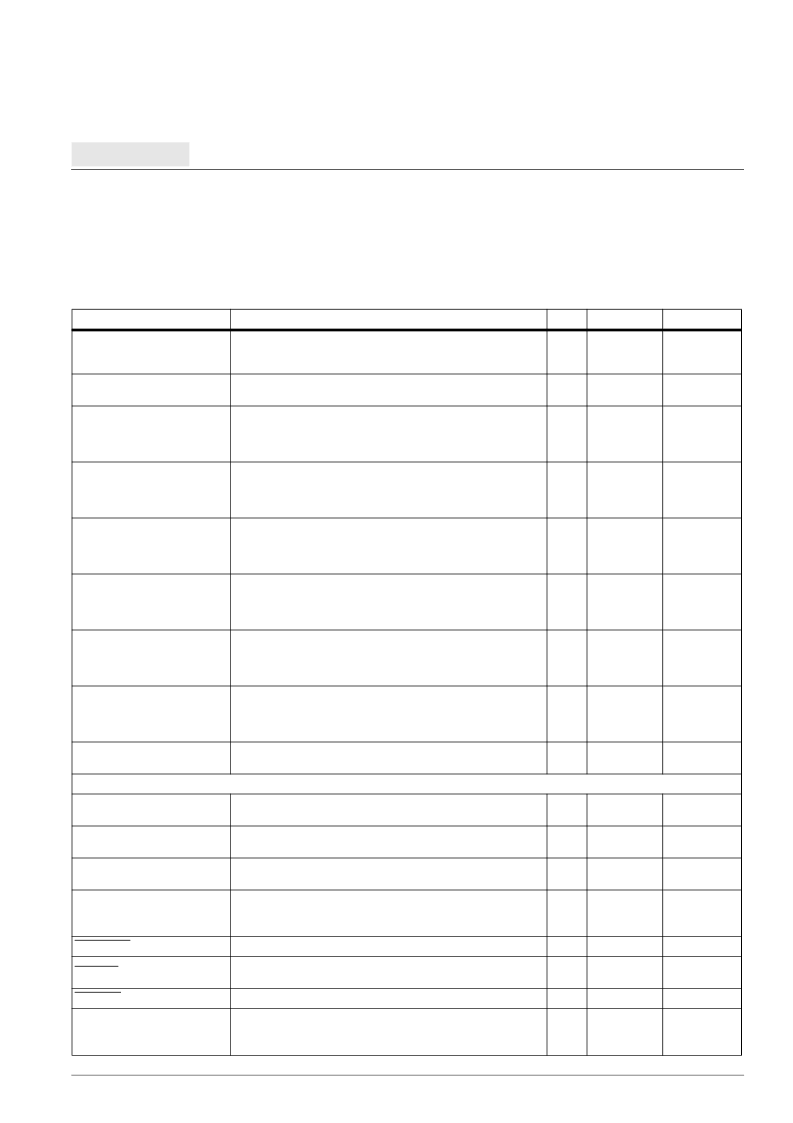

GMCCrS,

GMC1TxClk,

RTBI1TxClk

GMII: Carrier sense

RGMII: Transmit clock

RTBI: Transmit clock

I/O

3.3V tolerant

2.5V CMOS

GMCRefClk

GMII, RGMII, TBI and RTBI: Gigabit reference clock

I

3.3V tolerant

2.5V CMOS

5

GMCRxD0:3,

GMC0RxD0:3,

TBIRxD0:3,

RTBI0RxD0:3

GMII: Receive data

RGMII: Receive data

TBI: Receive data

RTBI: Receive data

I

3.3V tolerant

2.5V CMOS

GMCRxD4:7,

GMC1RxD0:3,

TBIRxD4:7,

RTBI1RxD0:3

GMII: Receive data

RGMII: Receive data

TBI: Receive data

RTBI: Receive data

I

3.3V tolerant

2.5V CMOS

GMCRxDV,

GMC0RxCtl,

TBIRxD8,

RTBI0RxD4

GMII: Receive data valid

RGMII: Receive control

TBI: Receive data

RTBI: Receive data

I

3.3V tolerant

2.5V CMOS

GMCRxEr,

GMC1RxCtl,

TBIRxD9,

RTBI1RxD4

GMII: Receive error

RGMII: Receive control

TBI: Receive data

RTBI: Receive data

I/O

3.3V tolerant

2.5V CMOS

GMCTxEn,

GMC0TxCtl,

TBITxD8,

RTBI0TxD4

GMII: Transmit data enable

RGMII: Transmit control

TBI: Transmit data

RTBI: Transmit data

O

3.3V tolerant

2.5V CMOS

GMCTxEr,

GMC1TxCtl,

TBITxD9,

RTBI1TxD4

GMII: Transmit error

RGMII: Transmit control

TBI: Transmit data

RTBI: Transmit data

O

3.3V tolerant

2.5V CMOS

6

GMCTxClk

TBIRxClk1

GMII: 10/100Mbps Transmit clock

TBI: Receive clock 1

I/O

3.3V LVTTL

5

External Slave Peripheral Interface

DMAAck0:3

Used by the PPC440GX to indicate that data transfers have

occurred.

O

3.3V tolerant

2.5V CMOS

DMAReq0:3

Used by slave peripherals to indicate they are prepared to transfer

data.

I

3.3V tolerant

2.5V CMOS

1, 5

EOT0:3/TC0:3

End Of Transfer/Terminal Count.

I/O

3.3V tolerant

2.5V CMOS

1, 5

PerAddr00:31

Peripheral address bus used by PPC440GX when not in external

master mode, otherwise used by external master.

Note:

PerAddr00 is the most significant bit (msb) on this bus.

I/O

3.3V LVTTL

1

PerWBE0:3

External peripheral data bus byte enables.

I/O

3.3V LVTTL

1, 2

PerBLast

Used by either the peripheral controller, DMA controller, or

external master to indicates the last transfer of a memory access.

I/O

3.3V LVTTL

1, 4

PerCS0:7

External peripheral device select.

O

3.3V LVTTL

2

PerData00:31

Peripheral data bus used by PPC440GX when not in external

master mode, otherwise used by external master.

Note:

PerData00 is the most significant bit (msb) on this bus.

I/O

3.3V LVTTL

1

Signal Functional Description

(Sheet 4 of 8)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

Ω

to 3.3V

)

3. Must pull down (recommended value is 1k

Ω

)

4. If not used, must pull up (recommended value is 3k

Ω

to 3.3V)

5. If not used, must pull down (recommended value is 1k

Ω

)

6. Strapping input during reset; pull-up or pull-down required

Signal Name

Description

I/O

Type

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC440GX-3CC667S | Power PC 440GX Embedded Processor |

| PPC440GX-3CF400C | Power PC 440GX Embedded Processor |

| PPC440GX-3CF533C | Power PC 440GX Embedded Processor |

| PPC440GX-3CF533CZ | Power PC 440GX Embedded Processor |

| PPC440GX-3CF533E | Power PC 440GX Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC440GX-3CC667C | 制造商:AppliedMicro 功能描述: |

| PPC440GX-3CC667S | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:Power PC 440GX Embedded Processor |

| PPC440GX-3CE800C | 制造商:AppliedMicro 功能描述: |

| PPC440GX-3CF400C | 制造商:AppliedMicro 功能描述:MPU 440GX RISC 32BIT 0.13UM 400MHZ 3.3V 552CBGA - Trays |

| PPC440GX-3CF533C | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:Power PC 440GX Embedded Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。