- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368096 > PPC440GRx-SpAfffTs (Applied Micro Circuits Corp.) PowerPC 440GRx Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC440GRx-SpAfffTs |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | PowerPC 440GRx Embedded Processor |

| 中文描述: | 嵌入式處理器的PowerPC 440GRx |

| 文件頁數(shù): | 85/88頁 |

| 文件大?。?/td> | 603K |

| 代理商: | PPC440GRX-SPAFFFTS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁當前第85頁第86頁第87頁第88頁

440GRx – PPC440GRx Embedded Processor

Revision 1.08 – October 15, 2007

Preliminary Data Sheet

AMCC Proprietary

85

Table 27. I/O Timing—DDR SDRAM T

SD

and T

HD

Notes:

1. T

SD

and T

HD

are measured under worst case conditions.

2. Clock speed for the values in the table is 166MHz.

3. The time values in the table include 1/4 of a cycle at 166MHz (6ns x 0.25 = 1.5 ns).

4. To obtain adjusted T

SD

and T

HD

values for lower clock frequencies, subtract 1.5 ns from the values in the table and add 1/4

of the cycle time for the lower clock frequency (for example, T

SD

1.5 + 0.25T

CYC

).

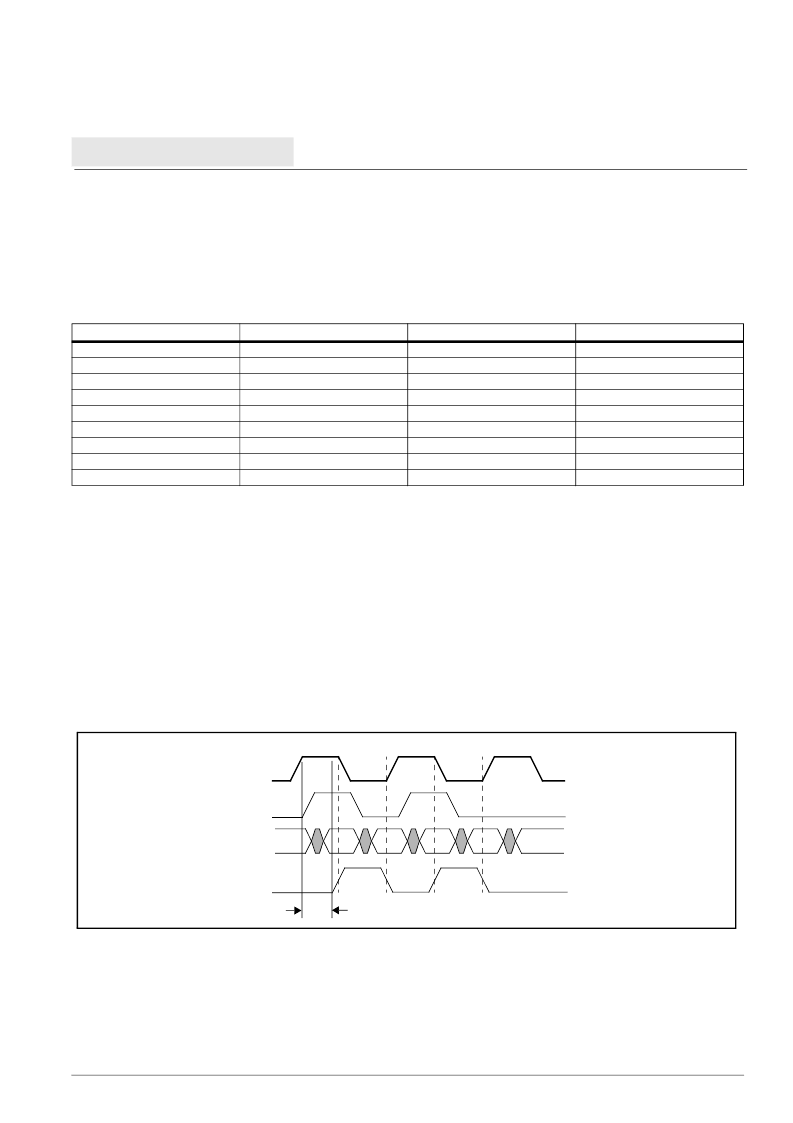

DDR SDRAM Read Operation

The read data capture logic is responsible for capturing the data outputs from the SDRAM devices and passing the

data back to the system clock domain. The data strobe signal (DQS) signals used to capture data are delayed to

ensure that the rising and falling edges of these strobes are in the middle of the valid window of data.

DDR devices send a DQS coincident with the read data so that the data can be reliably captured by the

PPC440GRx. The edges of these strobe signals are aligned with the data output by the SDRAM devices.

I

n order to reliably latch the data into a synchronizing FIFO, the PPC440GRx produces an internal, delayed version

of DQS. The amount of delay is user programmable. In the example shown in

Figure 12, DDR SDRAM DQS Read

Timing

, the delay is set to approximately 25% of the system clock. A delay compensation circuit in the PPC440GRx

keeps this delay constant.

Figure 12. DDR SDRAM DQS Read Timing

Signal Names

Reference Signal

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

T

SD

(ns)

1.37

1.41

1.40

1.41

1.45

1.40

1.46

1.45

1.46

T

HD

(ns)

1.23

1.18

1.17

1.20

1.18

1.18

1.17

1.10

1.18

MemData00:07, DM0

MemData08:15, DM1

MemData16:23, DM2

MemData24:31, DM3

MemData32:39, DM4

MemData40:47, DM5

MemData48:55, DM6

MemData56:63, DM7

ECC0:7, DM8

DQS delay

MemClkOut

DQS

MemData

Delayed DQS

(data strobe)

相關PDF資料 |

PDF描述 |

|---|---|

| PPC440GX-3RF800CZ | Power PC 440GX Embedded Processor |

| PPC440GX-3CC533S | Power PC 440GX Embedded Processor |

| PPC440GX-3CC667S | Power PC 440GX Embedded Processor |

| PPC440GX-3CF400C | Power PC 440GX Embedded Processor |

| PPC440GX-3CF533C | Power PC 440GX Embedded Processor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PPC440GRX-STA400E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-STA533E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-STA533EZ | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Tape and Reel |

| PPC440GRX-STA667E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-SUA400E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。