- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368096 > PPC440GRx-SpAfffTs (Applied Micro Circuits Corp.) PowerPC 440GRx Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC440GRx-SpAfffTs |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | PowerPC 440GRx Embedded Processor |

| 中文描述: | 嵌入式處理器的PowerPC 440GRx |

| 文件頁數(shù): | 55/88頁 |

| 文件大小: | 603K |

| 代理商: | PPC440GRX-SPAFFFTS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

440GRx – PPC440GRx Embedded Processor

Revision 1.08 – October 15, 2007

Preliminary Data Sheet

AMCC Proprietary

55

Multimode Signals

In some cases (for example, Ethernet) the function of a pin may vary with different modes of operation. When a pin

has multiple signal names assigned to distinguish different modes of operation, all of the names are shown.

Strapping Pins

One group of pins is used as strapped inputs during system reset. These pins function as strapped inputs only

during reset and are used for other functions during normal operation (see “Strapping” on page 86). Note that

these are

not multiplexed

pins since the function of the pins is not programmable.

Reserved Pins

The pins classified as Reserved are not functional and must be connected as shown in Table 8.

Unused I/Os

Termination of unused receivers is generally required; however, there are some exceptions that reduce or

eliminate the need for termination.

Signals Multiplexed with GPIO:

By default after reset, signals shared with GPIO pins are configured as GPIO receivers. Termination however,

is not needed if the GPIO during initialization are configured as outputs. To configure as drivers, set and clear

the appropriate bits in the GPIOx_ODR, GPIOx_TCR and GPIOx_OR registers as described in the GPIO

chapter of the user’s manual.

PCI:

When the PCI bridge is unused, configure the PCI controller to park on the bus by pulling the PCIReq0[Gnt]

signal low. Parking forces the PLB3 to PCI bridge to actively drive PCIAD31:0 and PCIC3:0[BE3:0]. The

remaining PCI control signals must be terminated as follows:

– Disable the internal PCI arbiter and enable PCI sychronous mode (See IIC Boot Strap Chapter in the

User’s Manual).

Note:

Synchronous mode is not supported when operating the PCI bus. This mode should only be used for

terminating an unused PCI interface).

– Individually connect PCISErr, PCIPErr, PCITRDY, and PCISTOP through 3k

Ω

resistors to +3.3V.

– Individually connect PCIReq1:5 through 3k

Ω

resistors to +3.3V.

– Connect PCIReq0[Gnt] through 1k

Ω

resistor to GND.

DDR:

– In 32 bit mode, termination is not needed on the upper data, strobe and mask signals when the DDR I/O

and DDR controller are configured for 32 bit mode, SDR0_DDRCFG[64B32B]=0 and

DDR0_14[REDUC=1.

– Termination of unused ECC signals (ECC0:7, DM8, DQS8) is not needed.

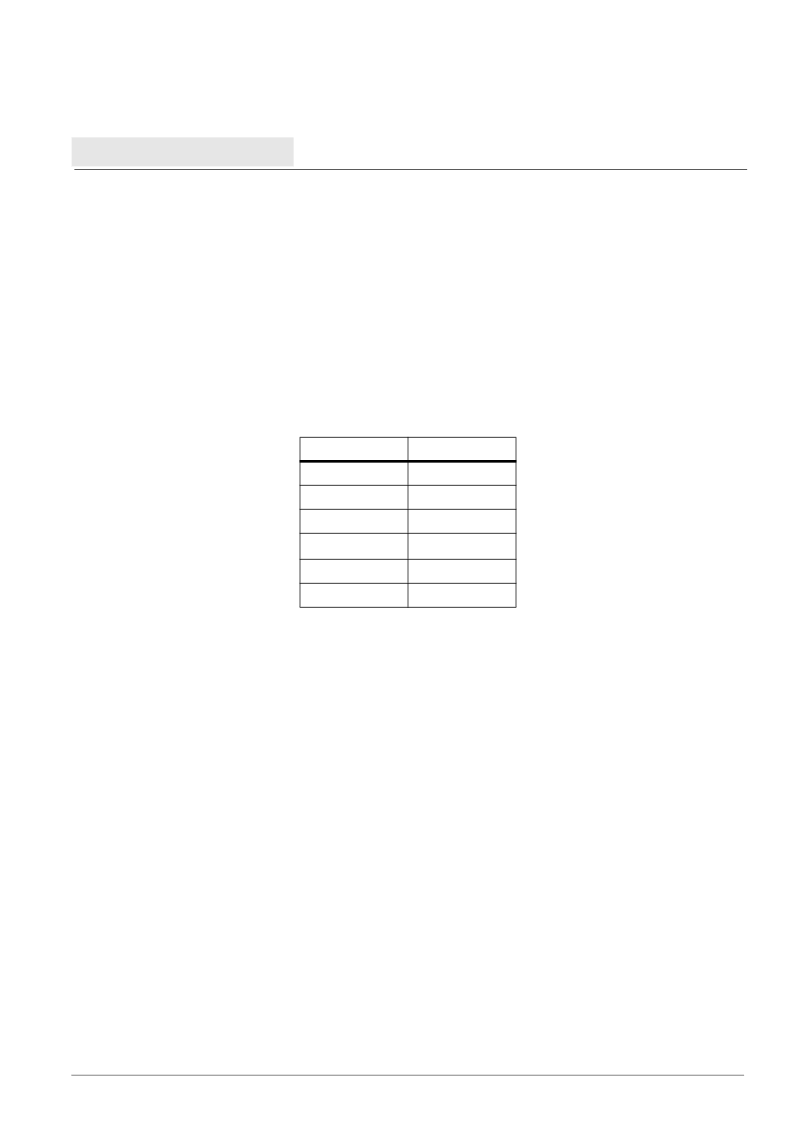

Table 8. Reserved Pin Connections

Pin

Connection

A05

GND

J01

Open

J02

Open

L03

OV

DD

N02

GND

N03

GND

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC440GX-3RF800CZ | Power PC 440GX Embedded Processor |

| PPC440GX-3CC533S | Power PC 440GX Embedded Processor |

| PPC440GX-3CC667S | Power PC 440GX Embedded Processor |

| PPC440GX-3CF400C | Power PC 440GX Embedded Processor |

| PPC440GX-3CF533C | Power PC 440GX Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC440GRX-STA400E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-STA533E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-STA533EZ | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Tape and Reel |

| PPC440GRX-STA667E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

| PPC440GRX-SUA400E | 制造商:AppliedMicro 功能描述:32 BIT POWERPC CORE, UP TO 667 MHZ, 2 10/100/1000 ETHERNET, - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。