- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3809 > PIC14000-04I/SP (Microchip Technology)IC MCU OTP 4KX14 A/D 28DIP PDF資料下載

參數(shù)資料

| 型號: | PIC14000-04I/SP |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 91/153頁 |

| 文件大小: | 0K |

| 描述: | IC MCU OTP 4KX14 A/D 28DIP |

| 產(chǎn)品培訓(xùn)模塊: | Asynchronous Stimulus 8-bit PIC® Microcontroller Portfolio |

| 標(biāo)準(zhǔn)包裝: | 15 |

| 系列: | PIC® 14 |

| 核心處理器: | PIC |

| 芯體尺寸: | 8-位 |

| 速度: | 4MHz |

| 連通性: | I²C |

| 外圍設(shè)備: | POR,溫度傳感器,WDT |

| 輸入/輸出數(shù): | 20 |

| 程序存儲器容量: | 7KB(4K x 14) |

| 程序存儲器類型: | OTP |

| RAM 容量: | 192 x 8 |

| 電壓 - 電源 (Vcc/Vdd): | 2.7 V ~ 6 V |

| 數(shù)據(jù)轉(zhuǎn)換器: | 斜率 A/D |

| 振蕩器型: | 內(nèi)部 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 28-DIP(0.300",7.62mm) |

| 包裝: | 管件 |

| 配用: | ISPICR1-ND - ADAPTER IN-CIRCUIT PROGRAMMING ICE2000-ND - EMULATOR MPLAB-ICE 2000 POD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁當(dāng)前第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁

PIC14000

DS40122B-page 42

Preliminary

1996 Microchip Technology Inc.

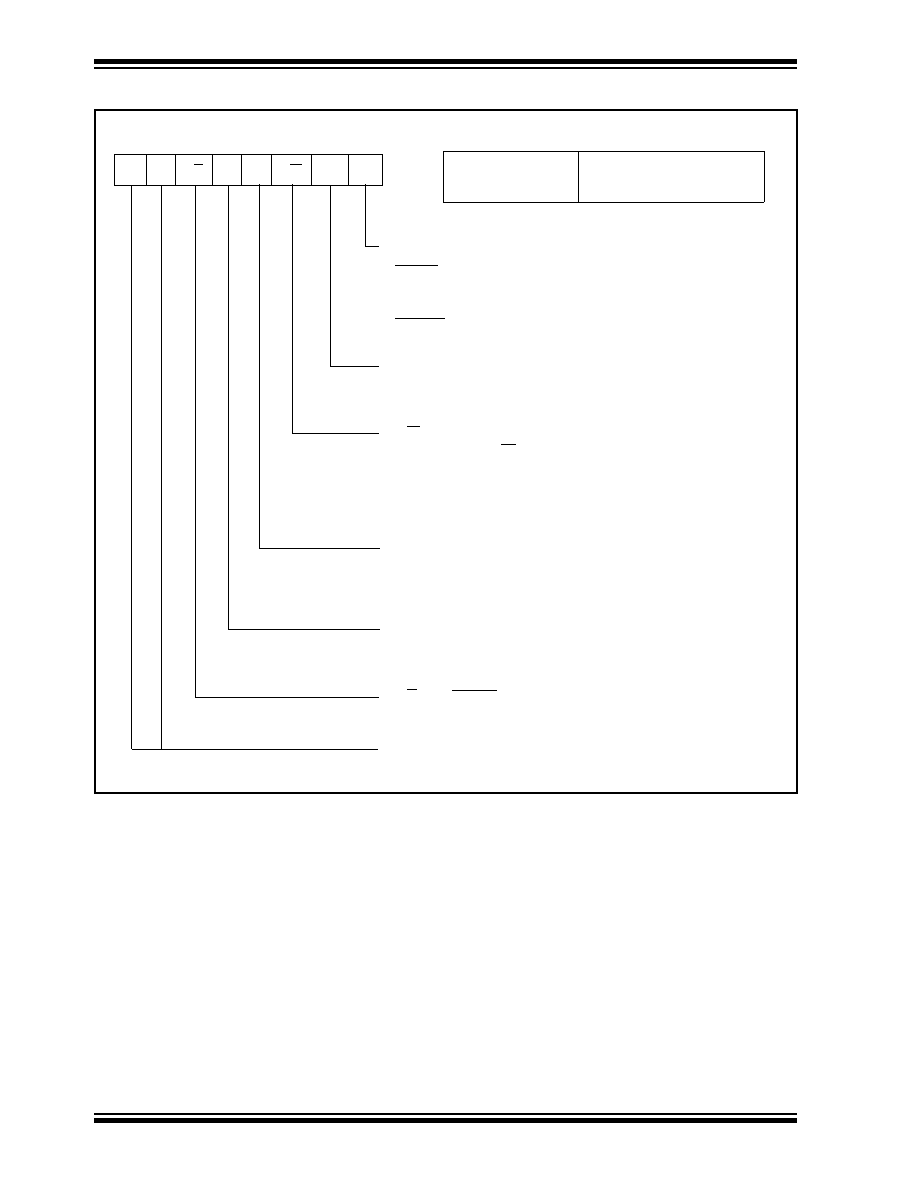

FIGURE 7-2:

I2CSTAT: I2C PORT STATUS REGISTER

BF: Buffer full

Receive

1 = Receive complete, I2CBUF is full

0 = Receive not complete, I2CBUF is empty

Transmit

1 = Transmit in progress, I2CBUF is full

0 = Transmit complete, I2CBUF is empty

UA: Update Address (10-bit I2C slave mode only)

1 = Indicate that the user needs to update the address in the I2CADD

register.

0 = Address does not need to be updated

R/

W: Read/write bit information

This bit holds the R/W bit information received following the last address

match. This bit is only valid during the transmission.

The user may use this bit in software to determine whether transmission

or reception is in progress.

1 = Read

0 = Write

S: Start bit

This bit is cleared when the I2C module is disabled (I2CEN is cleared)

1 = Indicates that a start bit has been detected last. This bit is 0 on

reset.

0 = Start bit was not detected last

P: Stop bit

This bit is cleared when the I2C module is disabled (I2CEN is cleared)

1 = Indicates that a stop bit has been detected last.

0 = Stop bit was not detected last

D/

A: Data/Address bit

1 = Indicates that the last byte received was data

0 = Indicates that the last byte received was address

Unimplemented: read as ‘0’

U

_

bit0

bit7

Register:

I2CSTAT

W: Writable bit

R

S

U

_

R

D/A

R

P

R

R/W

R

UA

R

BF

R: Readable bit

U: Unimplemented, read as ‘0’

Address:

94h

POR value:

00h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| C8051F231 | IC 8051 MCU 8K FLASH 32LQFP |

| C8051F230 | IC 8051 MCU 8K FLASH 48TQFP |

| C8051F226 | IC 8051 MCU 8K FLASH 48TQFP |

| 1-100526-3 | Z-PACK F.CODING KEY |

| 1-100526-2 | Z-PACK F.CODING KEY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PIC14000-20/SO | 功能描述:8位微控制器 -MCU 7KB 192 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| PIC14000-20/SP | 功能描述:8位微控制器 -MCU 7KB 192 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| PIC14000-20/SS | 功能描述:8位微控制器 -MCU 7KB 192 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| PIC14000-20I/P | 制造商:Microchip Technology Inc 功能描述:MCU 8BIT PIC14 RISC 7KB EPROM 5V - Bulk |

| PIC14000-20I/SO | 功能描述:8位微控制器 -MCU 7KB 192 RAM 20 I/O RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。