- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368020 > PI7C8152B PCI Bridge | Asynchronous 2-Port PCI Bridge PDF資料下載

參數(shù)資料

| 型號(hào): | PI7C8152B |

| 英文描述: | PCI Bridge | Asynchronous 2-Port PCI Bridge |

| 中文描述: | PCI橋|異步2端口PCI橋 |

| 文件頁數(shù): | 17/115頁 |

| 文件大?。?/td> | 879K |

| 代理商: | PI7C8152B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁

PI7C8150B

2-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 17 of 115

July 31, 2003 – Revision 1.031

CFG66 /

SCAN_EN_H /

CLK_RATE

125

K16

I

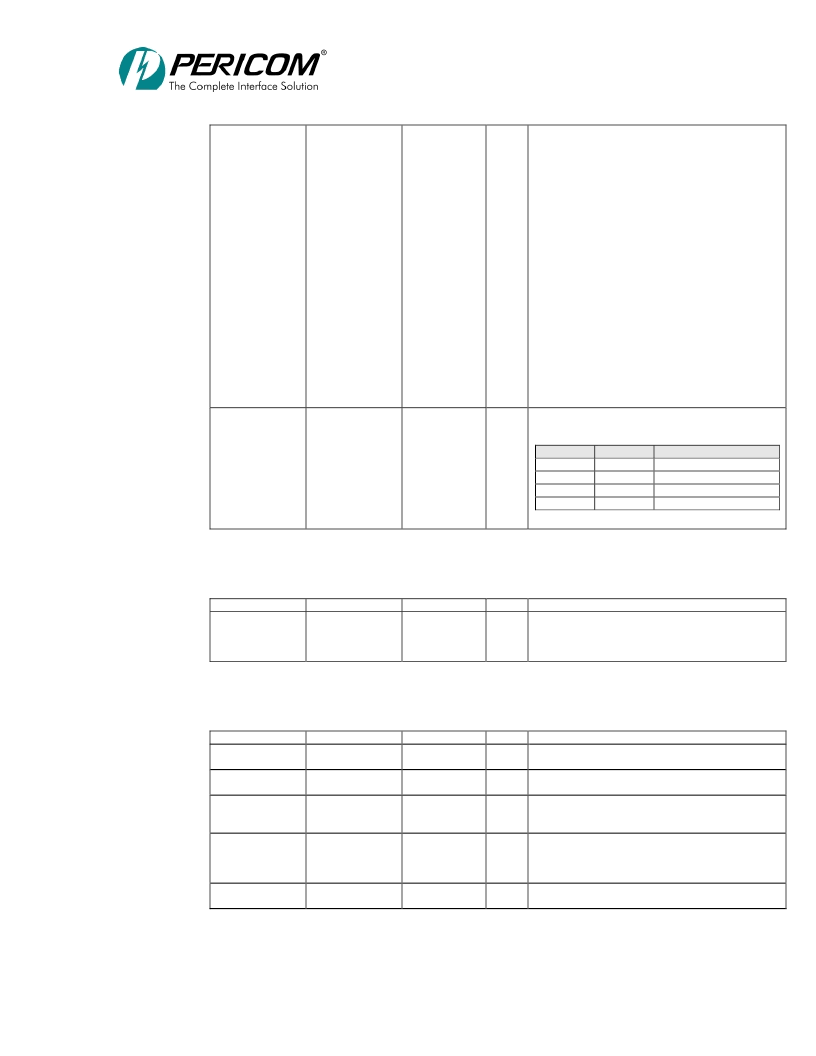

This is a multiplexed pin that has 3 functions (2 in

synchronous mode and 1 in asynchronous mode).

CFG66 - 66MHz Configuration (synchronous mode):

This pin is used to designate 66MHz operation. Tie

HIGH to enable 66MHz operation or tie LOW to

designate 33MHz operation.

SCAN_EN_H - Full-Scan Enable Control

(synchronous mode):

When SCAN_EN_H is LOW,

full-scan is in shift operation. When SCAN_EN_H is

HIGH, full-scan is in parallel operation.

Note: Valid only

in test mode. Pin is CFG66 in normal operation.

CLK_RATE – S_CLKOUT divider (asynchronous

mode):

Determines the S_CLKOUT frequency relation

to ASYNC_CLK_IN.

0: S_SCLKOUT is half the frequency of

ASYNC_CLK_IN.

1: S_CLKOUT is the same frequency as

ASYNC_CLK_IN.

Mode Selection:

Selector for Asynchronous or

Synchronous mode.

MS0

MS1

0

0

0

1

1

0

1

1

MS0, MS1

155, 106

B14, R16

I

Description

RESERVED

RESERVED

Synchronous Mode

Asynchronous Mode

2.2.5

GENERAL PURPOSE I/O INTERFACE SIGNALS

Name

GPIO[3:0]

Pin #

24, 25, 27, 28

Pin #

J3, J2, J1, K1

Type

TS

Description

General Purpose I/O Data Pins:

The 4 general-

purpose signals are programmable as either input-only

or bi-directional signals by writing the GPIO output

enable control register in the configuration space.

2.2.6

JTAG BOUNDARY SCAN SIGNALS

Name

TCK

Pin #

133

Pin #

H15

Type

I

Description

Test Clock.

Used to clock state information and data

into and out of the PI7C8150B during boundary scan.

Test Mode Select.

Used to control the state of the Test

Access Port controller.

Test Data Output.

When SCAN_EN_H is HIGH, it is

used (in conjunction with TCK) to shift data out of the

Test Access Port (TAP) in a serial bit stream.

Test Data Input.

When SCAN_EN_H is HIGH, it is

used (in conjunction with TCK) to shift data and

instructions into the Test Access Port (TAP) in a serial

bit stream.

Test Reset.

Active LOW signal to reset the Test Access

Port (TAP) controller into an initialized state.

TMS

132

H14

I

TDO

130

H16

O

TDI

129

J15

I

TRST_L

134

G15

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C8154 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8154-33 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150-33 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A | PCI Bridge | 2-Port PCI-to-PCI Bridge |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8152BEVB | 功能描述:界面開發(fā)工具 2 Port PCI to PCI Bridge Eval Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| PI7C8152BMA | 制造商:Pericom Semiconductor Corporation 功能描述:PCI to PCI Bridge 160-Pin MQFP |

| PI7C8152BMAE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PCI -to -PCI Bridge 2 Port RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8152BMAIE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 2 Port PCI to PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8154 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。