- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369995 > PF48F4P0VTQ0 (Intel Corp.) Intel StrataFlash Embedded Memory PDF資料下載

參數(shù)資料

| 型號(hào): | PF48F4P0VTQ0 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Embedded Memory |

| 中文描述: | 英特爾StrataFlash嵌入式存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 75/102頁(yè) |

| 文件大?。?/td> | 1609K |

| 代理商: | PF48F4P0VTQ0 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)當(dāng)前第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)

1-Gbit P30 Family

Datasheet

Intel StrataFlash

Embedded Memory (P30)

Order Number: 306666, Revision: 001

April 2005

75

14.0

Special Read States

The following sections describe non-array read states. Non-array reads can be performed in

asynchronous read or synchronous burst mode. A non-array read operation occurs as asynchronous

single-word mode. When non-array reads are performed in asynchronous page mode only the first

data is valid and all subsequent data are undefined. When a non-array read operation occurs as

synchronous burst mode, the same word of data requested will be output on successive clock edges

until the burst length requirements are satisfied.

Refer to the following waveforms for more detailed information:

Figure 16, “Asynchronous Single-Word Read (ADV# Low)” on page 38

Figure 17, “Asynchronous Single-Word Read (ADV# Latch)” on page 38

Figure 19, “Synchronous Single-Word Array or Non-array Read Timing” on page 39

14.1

Read Status Register

To read the Status Register, issue the Read Status Register command at any address. Status Register

information is available to which the Read Status Register, Word Program, or Block Erase

command was issued. Status Register data is automatically made available following a Word

Program, Block Erase, or Block Lock command sequence. Reads from the device after any of these

command sequences outputs the device’s status until another valid command is written (e.g. Read

Array command).

The Status Register is read using single asynchronous-mode or synchronous burst mode reads.

Status Register data is output on DQ[7:0], while 0x00 is output on DQ[15:8]. In asynchronous

mode the falling edge of OE#, or CE# (whichever occurs first) updates and latches the Status

Register contents. However, reading the Status Register in synchronous burst mode, CE# or ADV#

must be toggled to update status data.

The Device Write Status bit (SR[7]) provides overall status of the device. Status register bits

SR[6:1] present status and error information about the program, erase, suspend, V

PP

, and block-

locked operations.

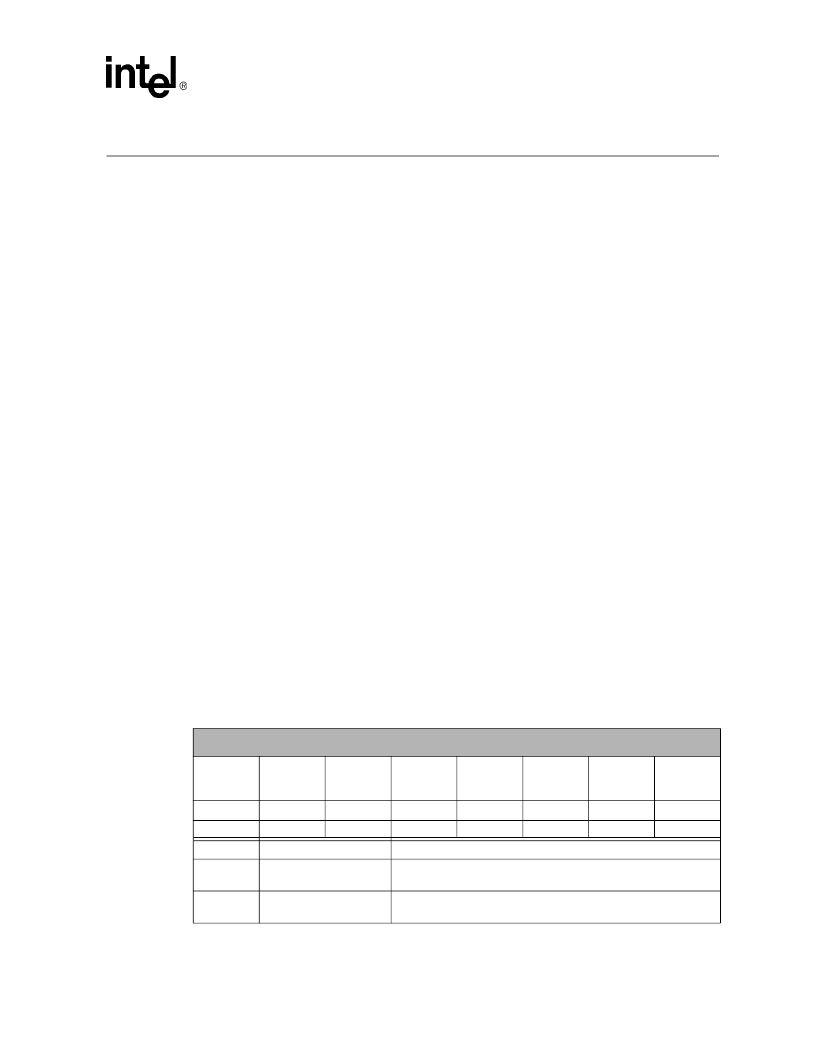

Table 28.

Status Register Description (Sheet 1 of 2)

Status Register (SR)

Default Value = 0x80

Device

Write Status

Erase

Suspend

Status

Erase

Status

Program

Status

V

PP

Status

Program

Suspend

Status

Block-

Locked

Status

BEFP

Status

DWS

ESS

ES

PS

VPPS

PSS

BLS

BWS

7

6

5

4

3

2

1

0

Bit

Name

Description

7

Device Write Status

(DWS)

0 = Device is busy; program or erase cycle in progress; SR[0] valid.

1 = Device is ready; SR[6:1] are valid.

6

Erase Suspend Status

(ESS)

0 = Erase suspend not in effect.

1 = Erase suspend in effect.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PF500A-360 | KPT SERIES |

| PF1000A | PFHC module 500W, 1000W |

| PF1000A-360 | PFHC module 500W, 1000W |

| PF5102 | N-Channel Switch |

| PF5103 | N-Channel Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PF48F4P0ZB00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0ZBQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0ZT00 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F4P0ZTQ0 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Embedded Memory |

| PF48F5000M0Y1BEA | 制造商:Micron Technology Inc 功能描述:512BA/0S SCSP 1.8 X16D HF B1 ADMUX - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。