- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369948 > PC28F640J3A-115 (Intel Corp.) Intel StrataFlash Memory (J3) PDF資料下載

參數(shù)資料

| 型號(hào): | PC28F640J3A-115 |

| 廠商: | Intel Corp. |

| 英文描述: | Intel StrataFlash Memory (J3) |

| 中文描述: | 英特爾StrataFlash存儲(chǔ)器(J3) |

| 文件頁(yè)數(shù): | 29/72頁(yè) |

| 文件大?。?/td> | 905K |

| 代理商: | PC28F640J3A-115 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

256-Mbit J3 (x8/x16)

Datasheet

29

7.4

Reset Operation

NOTE:

STS is shown in its default mode (RY/BY#).

7.5

AC Test Conditions

NOTE:

AC test inputs are driven at V

for a Logic "1" and 0.0 V for a Logic "0." Input timing begins, and

output timing ends, at V

CCQ

/2 V (50% of V

CCQ

). Input rise and fall times (10% to 90%) < 5 ns.

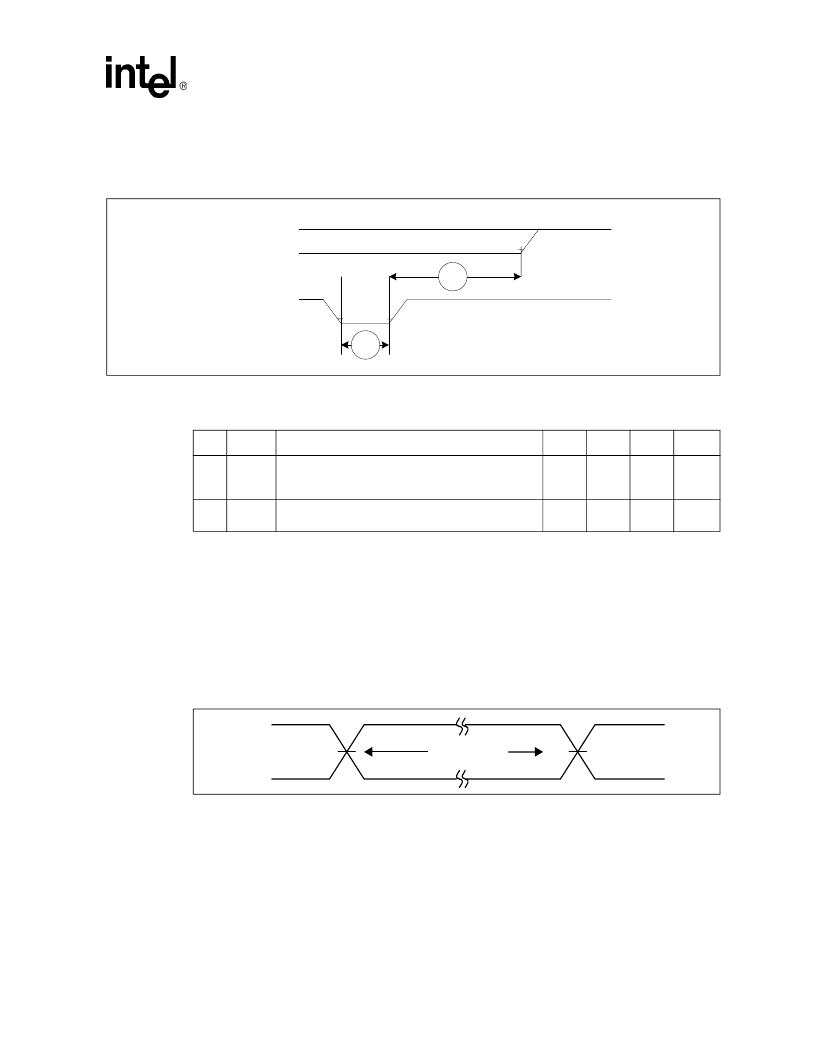

Figure 14. AC Waveform for Reset Operation

V

IH

V

IL

P1

V

IL

V

IH

P2

RP# (P)

STS (R)

Table 11. Reset Specifications

#

Sym

Parameter

Min

Max

Unit

Notes

P1

t

PLPH

RP# Pulse Low Time

(If RP# is tied to V

CC

, this specification is not

applicable)

35

μs

1,2

P2

t

PHRH

RP# High to Reset during Block Erase, Program, or

Lock-Bit Configuration

100

ns

1,3

NOTES:

1. These specifications are valid for all product versions (packages and speeds).

2. If RP# is asserted while a block erase, program, or lock-bit configuration operation is not

executing then the minimum required RP# Pulse Low Time is 100 ns.

3. A reset time, t

, is required from the latter of STS (in RY/BY# mode) or RP# going high until

outputs are valid.

Figure 15. Transient Input/Output Reference Waveform for V

CCQ

= 2.7 V–3.6 V

Output

Test Points

Input V

CCQ

/2

0.0

V

CCQ

V

CCQ

/2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC28F256J3A-115 | Intel StrataFlash Memory (J3) |

| PC28F256J3A-120 | Intel StrataFlash Memory (J3) |

| PC28F128J3A-150 | KPTC 32C 32#20 SKT PLUG |

| PC74HCT4002 | Dual 4-input NOR Gate |

| PCA24S08 | 1024 ?8-bit CMOS EEPROM with access protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC28F640J3A-120 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F640J3A-125 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F640J3A-150 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F640J3C-110 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel StrataFlash Memory (J3) |

| PC28F640J3C115 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。