- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224596 > NAND01GR3A2AZA6 (STMICROELECTRONICS) 128M X 8 FLASH 1.8V PROM, 15000 ns, PBGA63 PDF資料下載

參數(shù)資料

| 型號: | NAND01GR3A2AZA6 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | PROM |

| 英文描述: | 128M X 8 FLASH 1.8V PROM, 15000 ns, PBGA63 |

| 封裝: | 8.50 X 15 MM, 1.20 MM HEIGHT, 0.80 MM PITCH, TFBGA-63 |

| 文件頁數(shù): | 18/56頁 |

| 文件大?。?/td> | 871K |

| 代理商: | NAND01GR3A2AZA6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

25/56

NAND128-A, NAND256-A, NAND512-A, NAND01G-A

Cache Program

The Cache Program operation is used to improve

the programming throughput by programming

data using the Cache Register. The Cache Pro-

gram operation can only be used within one block.

The Cache Register allows new data to be input

while the previous data that was transferred to the

Page Buffer is programmed into the memory ar-

ray.

Before starting a Cache Program operation a

Pointer operation is necessary to point to the area

to be programmed. Only 00h Pointer operations

are valid before the Cache Program operation. Re-

fer to the Pointer Operations section and Figure

12. for details.

Each Cache Program operation consists of five

steps (refer to Figure 19.):

1.

First of all the program setup command is

issued (one bus cycle to issue the program

setup command then four bus write cycles to

input the address), the data is then input (up to

528 Bytes/ 264 Words) and loaded into the

Cache Register.

2.

One bus cycle is required to issue the confirm

command to start the P/E/R Controller.

3.

The P/E/R Controller then transfers the data to

the Page Buffer. During this the device is busy

for a time of tWHBH2.

4.

Once the data is loaded into the Page Buffer

the P/E/R Controller programs the data into

the memory array. As soon as the Cache

Registers are empty (after tWHBH2) a new

Cache program command can be issued,

while the internal programming is still

executing.

Once the program operation has started the Sta-

tus Register can be read using the Read Status

Register command. During Cache Program oper-

ations SR5 can be read to find out whether the in-

ternal programming is ongoing (SR5 = ‘0’) or has

completed (SR5 = ‘1’) while SR6 indicates wheth-

er the Cache Register is ready to accept new data.

If any errors have been detected on the previous

page (Page N-1), the Cache Program Error Bit SR1

will be set to ‘1', while if the error has been detect-

ed on Page N the Error Bit SR0 will be set to '1’.

When the next page (Page N) of data is input with

the Cache Program command, tWHBH2 is affected

by the pending internal programming. The data will

only be transferred from the Cache Register to the

Page Buffer when the pending program cycle is

finished and the Page Buffer is available.

If the system monitors the progress of the opera-

tion using only the Ready/Busy signal, the last

page of data must be programmed with the Page

Program confirm command (10h).

If the Cache Program confirm command (15h) is

used instead, Status Register bit SR5 must be

polled to find out if the last programming is finished

before starting any other operations.

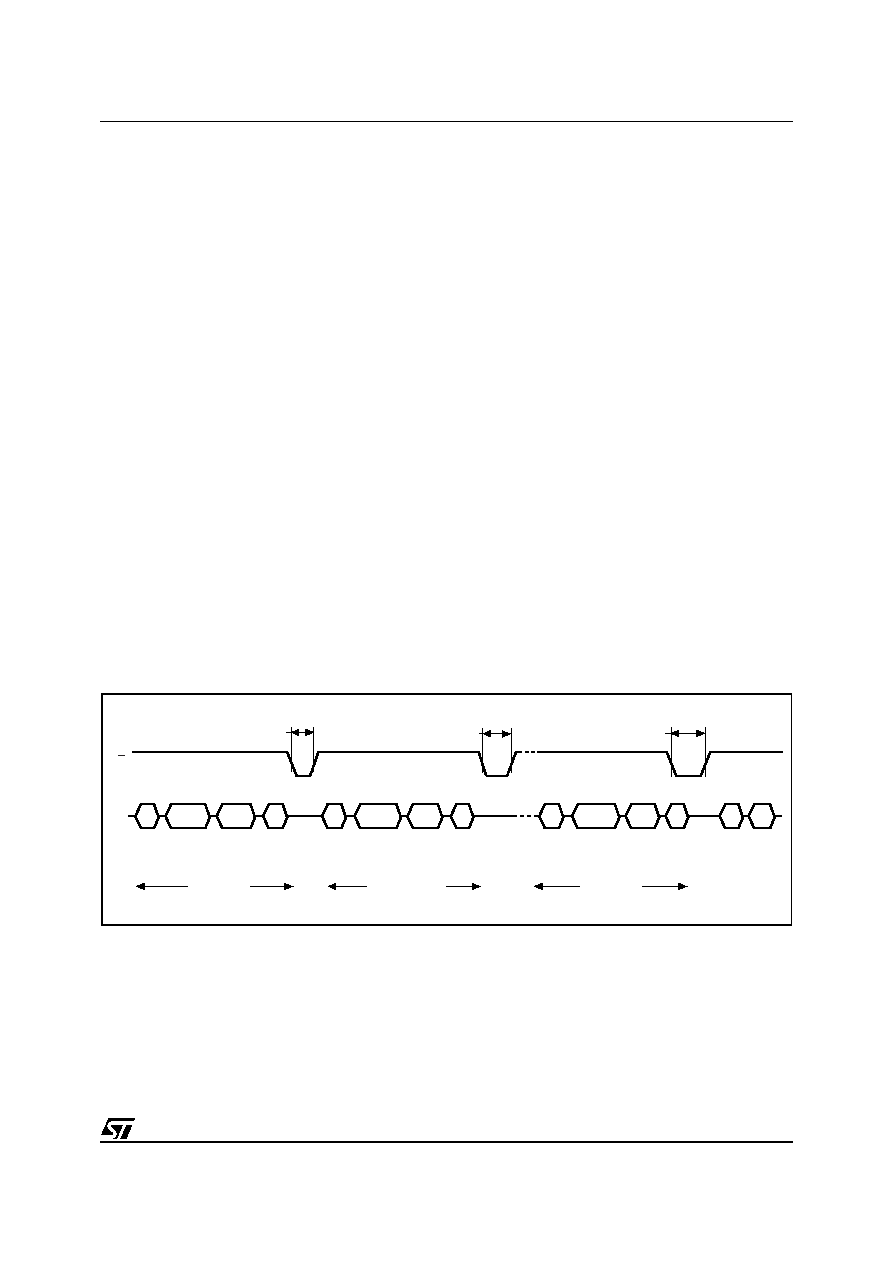

Figure 19. Cache Program Operation

Note: 1. Up to 32 pages can be programmed in one Cache Program operation.

2. tCACHEPG is the program time for the last page + the program time for the (last 1)

th page

(Program command cycle time + Last

page data loading time).

I/O

RB

Address

Inputs

ai07594c

80h

Page

Program

Code

Read Status

Register

Busy

Data

Inputs

15h

Cache

Program

Code

80h

Page

Program

Code

15h

Cache Program

Confirm Code

Busy

Last Page

tBLBH5

(Cache Busy time)

tBLBH5

tCACHEPG

SR0

70h

80h

10h

Page

Program

Confirm Code

Busy

First Page

Second Page

(can be repeated up to 30 times)

Address

Inputs

Data

Inputs

Address

Inputs

Data

Inputs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NAND01GR4B2BZA1F | 64M X 16 FLASH 1.8V PROM, 25000 ns, PBGA63 |

| NAND08GR4B3AZB6 | 512M X 16 FLASH 1.8V PROM, 25000 ns, PBGA63 |

| NAND256W4A2AZA6E | 16M X 16 FLASH 3V PROM, 12000 ns, PBGA55 |

| NCP303LSN41T1 | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO5 |

| NCS6416DWG | 8-CHANNEL, VIDEO MULTIPLEXER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| NAND01GR3A2AZA6E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Mbit, 256 Mbit, 512 Mbit, 1 Gbit (x8/x16) 528 Byte/264 Word Page, 1.8V/3V, NAND Flash Memories |

| NAND01GR3A2AZA6F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Mbit, 256 Mbit, 512 Mbit, 1 Gbit (x8/x16) 528 Byte/264 Word Page, 1.8V/3V, NAND Flash Memories |

| NAND01GR3A2AZA6T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Mbit, 256 Mbit, 512 Mbit, 1 Gbit (x8/x16) 528 Byte/264 Word Page, 1.8V/3V, NAND Flash Memories |

| NAND01GR3A2AZB1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Mbit, 256 Mbit, 512 Mbit, 1 Gbit (x8/x16) 528 Byte/264 Word Page, 1.8V/3V, NAND Flash Memories |

| NAND01GR3A2AZB1E | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:128 Mbit, 256 Mbit, 512 Mbit, 1 Gbit (x8/x16) 528 Byte/264 Word Page, 1.8V/3V, NAND Flash Memories |

發(fā)布緊急采購,3分鐘左右您將得到回復。