- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359243 > MVTX2802AG (ZARLINK SEMICONDUCTOR INC) Managed 4-Port 1000 Mbps Ethernet Switch PDF資料下載

參數(shù)資料

| 型號: | MVTX2802AG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 網(wǎng)絡接口 |

| 英文描述: | Managed 4-Port 1000 Mbps Ethernet Switch |

| 中文描述: | DATACOM, LAN SWITCHING CIRCUIT, PBGA596 |

| 封裝: | 40 X 40 MM, 2.33 MM HEIGHT, MS-034, HSBGA-596 |

| 文件頁數(shù): | 29/154頁 |

| 文件大?。?/td> | 1936K |

| 代理商: | MVTX2802AG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁

MVTX2802

Data Sheet

29

Zarlink Semiconductor Inc.

Also, when shaping is enabled, it is possible for a P6 queue to explode in length if fed by a greedy source. The

reason is that a shaper is by definition not work-conserving; that is, it may hold back from sending a packet

even if the line is idle. Though we do have global resource management, we do nothing to prevent this situation

locally. We assume SP traffic is policed at a prior stage to the MVTX2802AG.

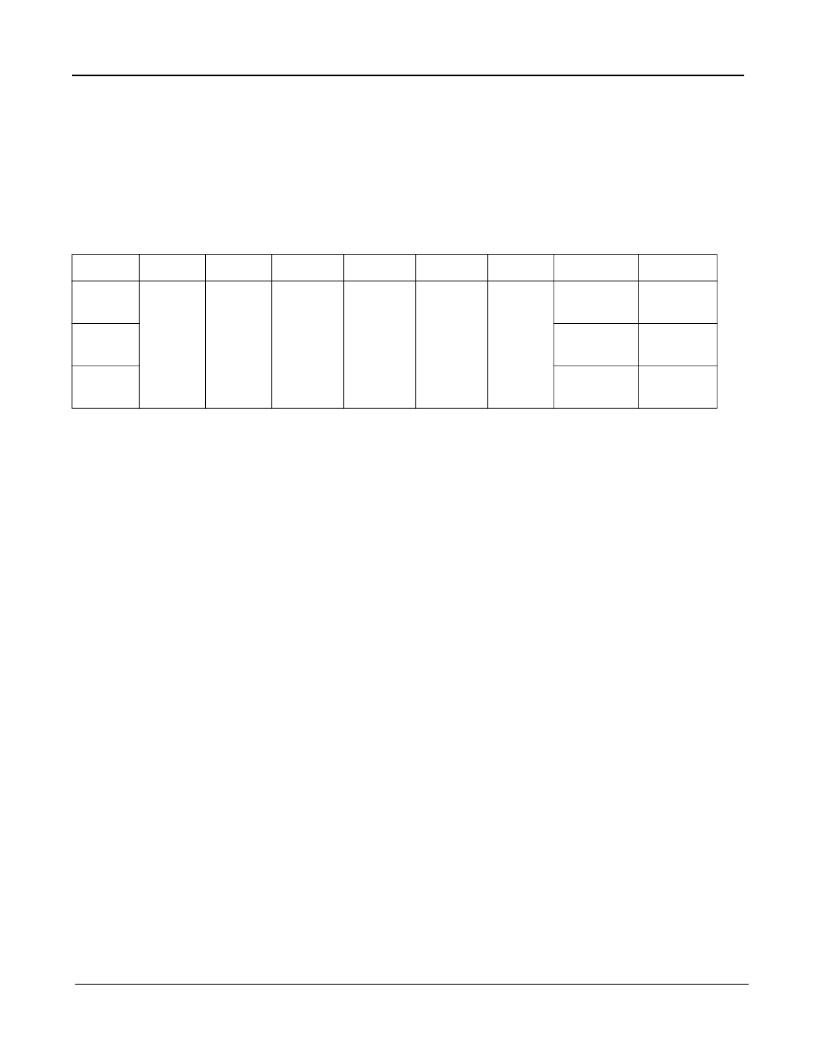

7.7 WRED Drop Threshold Management Support

To avoid congestion, the Weighted Random Early Detection (WRED) logic drops packets according to specified

parameters. The following table summarizes the behaviour of the WRED logic.

In the table, |Px| is the byte count in queue Px. The WRED logic has three drop levels, depending on the value of N,

which is based on the number of bytes in the priority queues. If delay bound scheduling is used, N equals 16|P7| +

16|P6| + 8|P5| + 4|P4| + 2|P3| + |P2|. If WFQ scheduling is used, N equals |P7| + |P6| + |P5| + |P4| + |P3| + |P2|.

Each drop level has defined high-drop and low-drop percentages, which indicate the percentage of high-drop and

low-drop packets that will be dropped at that level. The X, Y, and Z percent parameters can be programmed using

the registers RDRC0 and RDRC1. Parameters A-F are the byte count thresholds for each priority queue, and are

also programmable. When using delay bound scheduling, the values selected for A-F also control the approximate

bandwidth partition among the traffic classes; see application note.

7.8 Buffer Management

Because the number of frame data buffer (FDB) slots is a scarce resource, and because we want to ensure that

one misbehaving source port or class cannot harm the performance of a well-behaved source port or class, we

introduce the concept of buffer management into the MVTX2802AG. Our buffer management scheme is

designed to divide the total buffer space into numerous reserved regions and one shared pool (see Figure 5).

As shown in the figure, the FDB pool is divided into several parts. A reserved region for temporary frames

stores frames prior to receiving a switch response. Such a temporary region is necessary, because when the

frame first enters the MVTX2802AG, its destination port and class are as yet unknown, and so the decision to

drop or not needs to be temporarily postponed. This ensures that every frame can be received first before

subjecting it to the frame drop discipline after classifying.

Six reserved sections, one for each of the highest six priority classes, ensure a programmable number of FDB

slots per class. The lowest two classes do not receive any buffer reservation.

Another segment of the FDB reserves space for each of the 4 Gigabit ports and CPU port. These source port

buffer reservations are programmable. These 9 reserved regions make sure that no well-behaved source port

can be blocked by another misbehaving source port.

P7

P6

P5

P4

P3

P2

High Drop

Low Drop

Level 1

N

≥

240

|P7|

≥

A

KB

|P6|

≥

B

KB

|P5|

≥

C

KB

|P4|

≥

D

KB

|P3|

≥

E

KB

|P2|

≥

F

KB

X%

0%

Level 2

N

≥

280

Y%

Z%

Level 3

N

≥

320

100%

100%

Table 3 - WRED Dropping Scheme

相關PDF資料 |

PDF描述 |

|---|---|

| MVTX2803 | Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803AG | Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2804 | 8-Port 1000 Mbps Ethernet Distributed Switch |

| MVTX2804AG | 8-Port 1000 Mbps Ethernet Distributed Switch |

| MVV200 | Analog IC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MVTX2803 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Unmanaged 8 port Gigabit Ethernet switch |

| MVTX2803AG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803AG2 | 制造商:Microsemi Corporation 功能描述: |

| MVTX2804 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:8-Port 1000 Mbps Ethernet Distributed Switch |

發(fā)布緊急采購,3分鐘左右您將得到回復。