- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359243 > MVTX2802AG (ZARLINK SEMICONDUCTOR INC) Managed 4-Port 1000 Mbps Ethernet Switch PDF資料下載

參數(shù)資料

| 型號(hào): | MVTX2802AG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類(lèi): | 網(wǎng)絡(luò)接口 |

| 英文描述: | Managed 4-Port 1000 Mbps Ethernet Switch |

| 中文描述: | DATACOM, LAN SWITCHING CIRCUIT, PBGA596 |

| 封裝: | 40 X 40 MM, 2.33 MM HEIGHT, MS-034, HSBGA-596 |

| 文件頁(yè)數(shù): | 20/154頁(yè) |

| 文件大?。?/td> | 1936K |

| 代理商: | MVTX2802AG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)

MVTX2802

Data Sheet

20

Zarlink Semiconductor Inc.

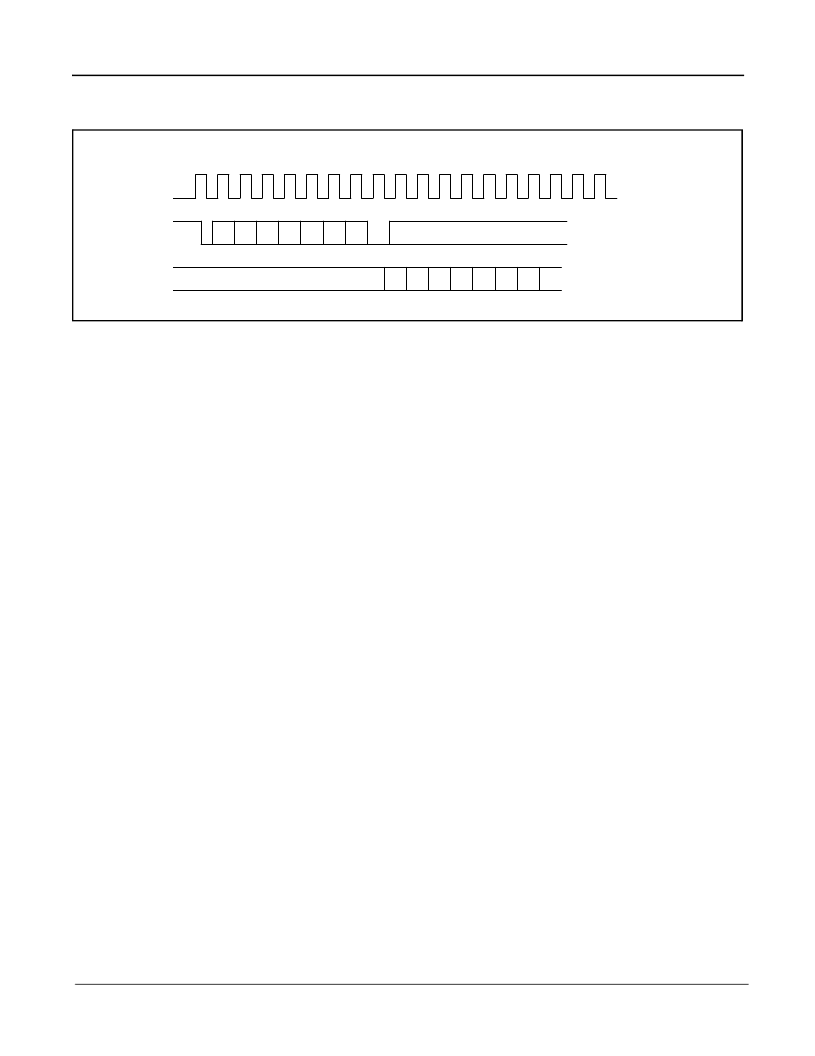

2.6.2 Read Command

All registers in the MVTX2802AG can be modified through this synchronous serial interface.

3.0 Data Forwarding Protocol

3.1 Unicast Data Frame Forwarding

When a frame arrives, it is assigned a handle in memory by the Frame Control Buffer Manager (FCB Manager).

An FCB handle will always be available, because of advance buffer reservations.

The memory (ZBT-SRAM) interface is a 64-bit bus, connected to a ZBT-SRAM domain. The Receive DMA

(RxDMA) is responsible for multiplexing the data and the address. On a port’s “turn,” the RxDMA will move 8

bytes (or up to the end-of-frame) from the port’s associated RxFIFO into memory (Frame Data Buffer, or FDB).

Once an entire frame has been moved to the FDB, and a good end-of-frame (EOF) has been received, the Rx

interface makes a switch request. The RxDMA arbitrates among multiple switch requests.

The switch request consists of the first 64 bytes of a frame, containing among other things, the source and

destination MAC addresses of the frame. The search engine places a switch response in the switch response

queue of the frame engine when done. Among other information, the search engine will have resolved the

destination port of the frame and will have determined that the frame is unicast.

After processing the switch response, the Transmission Queue Manager (TxQ manager) of the frame engine is

responsible for notifying the destination port that it has a frame to forward to it. But first, the TxQ manager has

to decide whether or not to drop the frame, based on global FDB reservations and usage, as well as TxQ

occupancy at the destination. If the frame is not dropped, then the TxQ manager links the frame’s FCB to the

correct per-port-per-class TxQ. Unicast TxQ’s are linked lists of transmission jobs, represented by their

associated frames’ FCB’s. There is one linked list for each transmission class for each port. There are 8 classes

for each of the 4 Gigabit ports – a total of 32 unicast queues.

The TxQ manager is responsible for scheduling transmission among the queues representing different classes

for a port. When the port control module determines that there is room in the MAC Transmission FIFO (TxFIFO)

for another frame, it requests the handle of a new frame from the TxQ manager. The TxQ manager chooses

among the head-of-line (HOL) frames from the per-class queues for that port, using a Zarlink Semiconductor

scheduling algorithm.

As at the transmit end, each of the 4 ports has time slots devoted solely to reading data from memory at the

address calculated by port control. The Transmission DMA (TxDMA) is responsible for multiplexing the data and

the address. On a port’s turn, the TxDMA will move 8 bytes (or up to the EOF) from memory into the port’s

associated TxFIFO. After reading the EOF, the port control requests a FCB release for that frame. The TxDMA

arbitrates among multiple buffer release requests.

The frame is transmitted from the TxFIFO to the line.

PS_STROBE-

PS_DI

PS_DO

A0

A1

A2

...

A9

A10

A11

R

D0

D1

D2

D3

D4

D5

D6

D7

START

ADDRESS

COMMAND

DATA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MVTX2803 | Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803AG | Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2804 | 8-Port 1000 Mbps Ethernet Distributed Switch |

| MVTX2804AG | 8-Port 1000 Mbps Ethernet Distributed Switch |

| MVV200 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MVTX2803 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Unmanaged 8 port Gigabit Ethernet switch |

| MVTX2803AG | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:Unmanaged 8-Port 1000 Mbps Ethernet Switch |

| MVTX2803AG2 | 制造商:Microsemi Corporation 功能描述: |

| MVTX2804 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:8-Port 1000 Mbps Ethernet Distributed Switch |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。