- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT9315 (Zarlink Semiconductor Inc.) CMOS Acoustic Echo Canceller PDF資料下載

參數(shù)資料

| 型號(hào): | MT9315 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | CMOS Acoustic Echo Canceller |

| 中文描述: | 聲學(xué)回聲消除器的CMOS |

| 文件頁(yè)數(shù): | 3/30頁(yè) |

| 文件大小: | 361K |

| 代理商: | MT9315 |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

MT9315

Advance Information

2

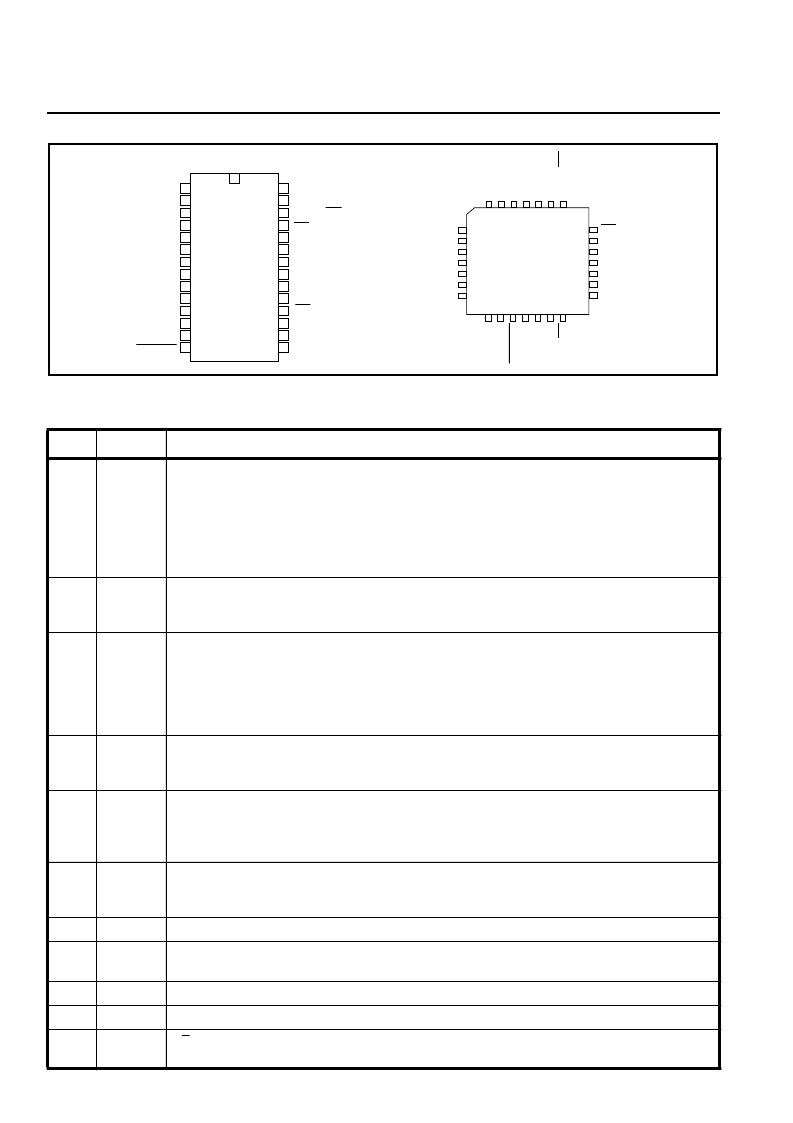

Figure 2 - Pin Connections

Pin Description

Pin #

Name

Description

1

ENA1

SSI Enable Strobe / ST-BUS Mode for Rin/Sout (Input)

. This pin has dual functions

depending on whether SSI or ST-BUS is selected.

For SSI, this strobe must be present for frame synchronization. This is an active high channel

enable strobe, 8 or 16 data bits wide, enabling serial PCM data transfer for on Rin/Sout pins.

Strobe period is 125 microseconds.

For ST-BUS, this pin, in conjunction with the MD1 pin, will select the proper ST-BUS mode for

Rin/Sout pins (see ST-BUS Operation description).

2

MD1

ST-BUS Mode for Rin/Sout (Input)

. When in ST-BUS mode, this pin, in conjunction with the

ENA1 pin, will select the proper ST-BUS mode for Rin/Sout pins (see ST-BUS Operation

description). Connect this pin to Vss in SSI mode.

3

ENA2

SSI Enable Strobe / ST-BUS Mode for Sin/Rout (Input)

.This pin has dual functions

depending on whether SSI or ST-BUS is selected.

For SSI, this is an active high channel enable strobe, 8 or 16 data bits wide, enabling serial

PCM data transfer on Sin/Rout pins. Strobe period is 125 microseconds.

For ST-BUS, this pin, in conjunction with the MD2 pin, will select the proper ST-BUS mode for

Sin/Rout pins (see ST-BUS Operation description).

4

MD2

ST-BUS Mode for Sin/Rout (Input)

.When in ST-BUS mode, this pin in conjunction with the

ENA2 pin, will select the proper ST-BUS mode for Sin/Rout pins (see ST-BUS Operation

description). Connect this pin to Vss in SSI mode.

5

Rin

Receive PCM Signal Input (Input).

128 kbit/s to 4096 kbit/s serial PCM input stream. Data

may be in either companded or 2’s complement linear format. This is the Receive Input

channel from the line (or line) side. Data bits are clocked in following SSI or ST-BUS timing

requirements.

6

Sin

Send PCM Signal Input (Input).

128 kbit/s to 4096 kbit/s serial PCM input stream. Data may

be in either companded or 2’s complement linear format. This is the Send Input channel (from

the microphone). Data bits are clocked in following SSI or ST-BUS timing requirements.

7

VSS

Digital Ground:

Nominally 0 volt.

8

MCLK

Master Clock (Input):

Nominal 20 MHz Master Clock input. May be connected to an

asynchronous (relative to frame signal) clock source.

9

IC

Internal Connection (Input):

Must be tied to Vss.

10, 11

IC

Internal Connection (Input).

Tie to Vss.

12

LAW

A/

μ

Law Select (Input).

When low, selects

μ

Law companded PCM. When high, selects A-

Law companded PCM. This control is for both serial pcm ports.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

DATA2

CS

VDD

NC

DATA1

IC

IC

IC

NC

NC

SCLK

Sout

Rout

BCLK/C4i

F0i

IC

IC

Sin

VSS

MCLK

Rin

MD2

MD1

ENA2

FORMAT

PWRDN

LAW

ENA1

M

M

E

E

B

I

I

IC

IC

IC

Sin

VSS

Rin

F

L

P

N

N

S

C

DATA2

VDD

NC

DATA1

Sout

Rout

F0i

PLCC

4

5

6

7

8

9

10

11

25

24

23

22

21

20

19

3

2

1

2

2

2

1

1

1

1

1

1

1

PDIP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT933 | 3.3V 10/100 Fast Ethernet Transceiver to MII |

| MT933CG | 3.3V 10/100 Fast Ethernet Transceiver to MII |

| MT933TP1N | 3.3V 10/100 Fast Ethernet Transceiver to MII |

| MT93L00A | Multi-Channel Voice Echo Canceller |

| MT93L04 | 128-Channel Voice Echo Canceller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9315AE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:CMOS Acoustic Echo Canceller |

| MT9315AP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:CMOS Acoustic Echo Canceller |

| MT933 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:3.3V 10/100 Fast Ethernet Transceiver to MII |

| MT933CG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:3.3V 10/100 Fast Ethernet Transceiver to MII |

| MT933TP1N | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:3.3V 10/100 Fast Ethernet Transceiver to MII |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。