- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359233 > MT8930CE (ZARLINK SEMICONDUCTOR INC) Subscriber Network Interface Circuit PDF資料下載

參數(shù)資料

| 型號: | MT8930CE |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | Subscriber Network Interface Circuit |

| 中文描述: | DATACOM, DIGITAL SLIC, PDIP28 |

| 封裝: | PLASTIC, MS-011AB, DIP-28 |

| 文件頁數(shù): | 14/41頁 |

| 文件大小: | 2516K |

| 代理商: | MT8930CE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

MT8930C

Data Sheet

14

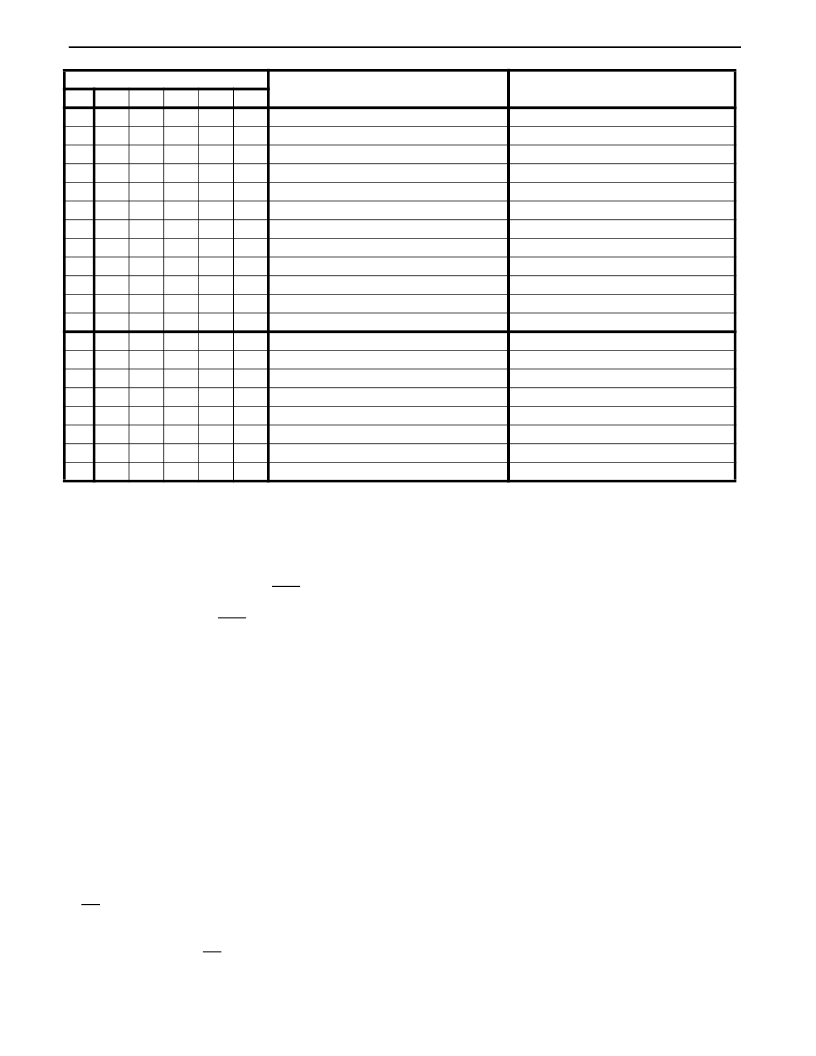

Table 2. SNIC Address Map

Address Lines

A3

0

0

0

0

0

0

0

0

1

1

0

0

1

1

1

1

1

1

1

1

Write

Read

A4

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

A2

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

A1

0

0

1

1

0

0

1

1

0

0

0

1

0

0

1

1

0

0

1

1

A0

0

1

0

1

0

1

0

1

0

1

0

0

0

1

0

1

0

1

0

1

Master Control Register

ST-BUS Control Register

HDLC Control Register 1

HDLC Control Register 2

HDLC Interrupt Mask Register

HDLC Tx FIFO

HDLC Address Byte #1 Register

HDLC Address Byte #2 Register

C-channel Control Register

verify

verify

verify

A

S

Y

N

C

HDLC Status Register

HDLC Interrupt Status Register

HDLC Rx FIFO

verify

verify

C-channel Status Register

Not available

Master Status Register

DSTi C-channel

Control Register 1

Not Available

DSTo C-channel

S-Bus Tx D-channel

DSTo D-channel

S-Bus Tx B1-channel

DSTo B1-channel

S-Bus Tx B2-channel

DSTo B2-channel

S

Y

N

C

DSTi D-channel

S-Bus Rx D-channel

DSTi B1-channel

S-Bus Rx B1-channel

DSTi B2-channel

S-Bus Rx B2-channel

Some registers are classified as asynchronous and

others as synchronous. Synchronous registers are

single-buffered and require synchronous access.

Not all the synchronous registers have the same

access times, but all can be accessed synchronously

in the time during which the NDA signal is low

(refer to Fig. 5). Therefore, it is recommended that

the user make use of the NDA signal to access these

registers. Since the synchronous registers use

common circuitry, it is essential that the register be

read before being written. This sequence is

important as a write cycle will overwrite the last data

received. These parallel accesses must be refreshed

every frame. Asynchronous registers, on the other

hand, can be accessed at any time.

When the Cmode pin is low, controllerless mode is

selected and the parallel port reverts to hardwired

control/status pins. This allows the MT8930C to

function without the need for a controlling

microprocessor. In the controllerless mode, the

parallel bus has direct connection to the relevant

control/status registers (refer to Pin Description).

Discrete logic can be used to drive/sense

the respective pins. In this mode, pin 11

(P/SC determines whether the microport pins or

the C-channel bits on DSTi stream are the control

source of the device. If the C-channel is selected

to be the source, P/SC is tied low, then the

microport pins are ignored and the C-channel is

loaded into the C-channel Control Register.

The data in TE or NT Mode Status Register,

depending upon the mode selected, is always sent

out on the C-channel of DSTo. However, in

microprocessor control mode the user can overwrite

this data by writing to the DSTo C-channel Register.

This access can be done anytime outside the frame

pulse interval of the ST-BUS frame. Data written in

the current ST-BUS frame will only appear in the C-

channel of the following frame.

The least significant bit (B0) of the C-channel

Register, selects between the control register or the

diagnostic register. Setting the B0 of the C-channel

Register to ’0’ allow access to the control register.

Setting the LSB of the C-channel Register to ’1’ allow

access to the diagnostic register. The interpretation

of each register is defined in Tables 13 and 14 for NT

mode or Tables 16 and 17 for the TE mode.

It is important to note that in TE mode, the C-channel

Diagnostic Register should be cleared while the

device is not in the active state (IS0, IS1

≠

1,1). This

is accomplished by setting the ClrDia bit of the C-

channel Control Register to 1 until the device is

activated. In serial control mode, the C-channel on

the ST-BUS is loaded into the C-channel Control

Register in every ST-BUS frame; the user should

make sure that a 1 is written to the ClrDia bit in every

frame. However, in parallel control mode the user

needs to set the ClrDia bit only once to keep the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8930CP | Subscriber Network Interface Circuit |

| MT8931C | Subscriber Network Interface Circuit |

| MT8931CE | Subscriber Network Interface Circuit |

| MT8931CP | Subscriber Network Interface Circuit |

| MT8931C-1 | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8930CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CPR | 制造商:Microsemi Corporation 功能描述: |

| MT8931B | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

| MT8931BC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

| MT8931BE | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。