- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378018 > MSM82C37B-5GS (OKI SEMICONDUCTOR CO., LTD.) PROGRAMMABLE DMA CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | MSM82C37B-5GS |

| 廠商: | OKI SEMICONDUCTOR CO., LTD. |

| 英文描述: | PROGRAMMABLE DMA CONTROLLER |

| 中文描述: | 可編程DMA控制器 |

| 文件頁數(shù): | 12/34頁 |

| 文件大?。?/td> | 301K |

| 代理商: | MSM82C37B-5GS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

12/33

Semiconductor

MSM82C37B-5RS/GS/VJS

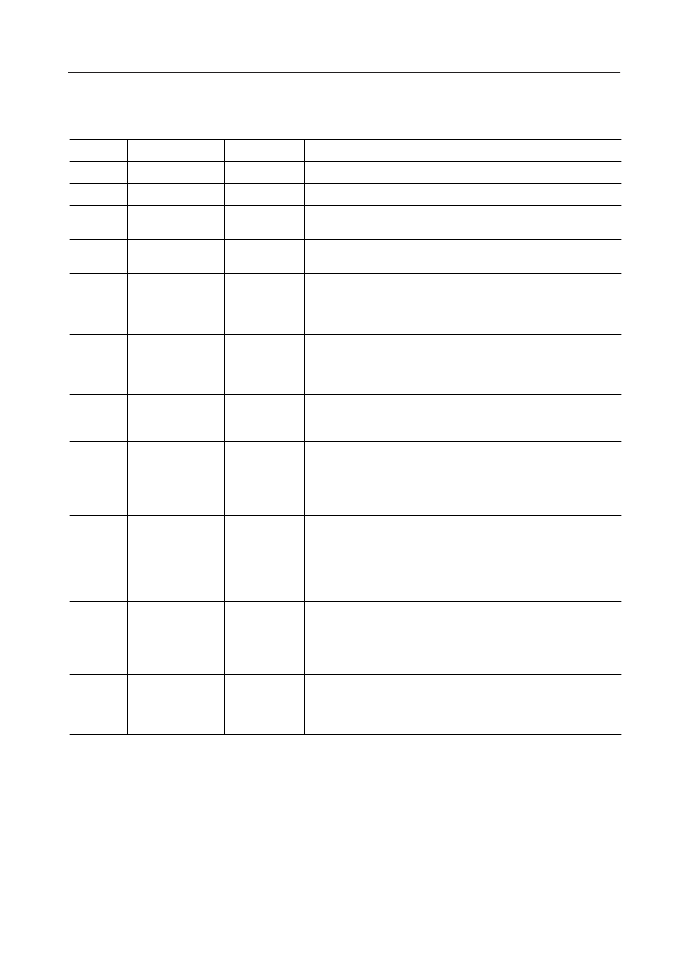

PIN FUNCTIONS

Power

V

CC

GND

Symbol

Pin Name

—

Input/Output

Function

+5 V power supply

Ground

—

Ground (0 V) connection.

Clock

CLK

Input

Control of MSM82C37B-5 internal operations and data transfer

speed.

CS

is active-low input signal used for the CPU to select

the MSM82C37B-5 as an I/O device in an idle cycle.

Chip Select

CS

Input

Hold Acknowledge

HLDA

Input

HLDA is active-high input signal used to indicate that system bus

control has been released when a hold request is recieved by

the CPU.

DREQ is asynchronous DMA transfer request input signals.

Although these pins are switched to active-high by reset, they can

be programmed to become active-low. DMA requests are

received in accordance with a prescribed order of priority. DREQ

must be held until DACK becomes active.

DB is bidirectional three-state signals connected to the system

data bus, and which is used as an input/output of MSM82C37B-5

internal registers during idle cycles, and as an output of the eight

higher order bits of transfer addresses during active cycles.

Also used as input and output of transfer data during memory-

memory transfers.

Reset

RESET

Input

RESET is active-high asynchrounous input signal used to clear

command, status, request, temporary registers, and first/last F/F,

and to set mask register. The MSM82C37B-5 enters an idle cycle

following a RESET.

Ready

READY

Input

The read or write pulse width can be extended to accomodate

slow access memories and I/O devices when this input is

switched to low level. Note this input must not change within

the prescribed set-up/hold time.

I/O Read

IOR

Input/Output

IOR

is active-low bidirectional three-state signal used as an input

control signal for CPU reading of MSM82C37B-5 internal

registers during idle cycles, and as an output control signal for

reading I/O device transfer data in writing transfers during active

cycles.

IOW

is active-low bidirectional three-state signal used as an input

control signal for CPU writing of MSM82C37B-5 internal registers

during idle cycles, and as an output control signal for writing I/O

device transfer data in writing transfers during active cycles.

I/O Write

IOW

Input/Output

DMA Request

0 - 3 Channels

DREQ

0

-

DREQ

3

Input

Data Bus 0 - 7

DB

0

- DB

7

Input/Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM82C43 | INPUT/OUTPUT PORT EXPANDER |

| MSM82C51A-2GS | UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER |

| MSM82C51A-2JS | UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER |

| MSM82C51A-2RS | UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER |

| MSM82C59A-2GS | PROGRAMMABLE INTERRUPT CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM82C37B-5JS | 制造商:OK International 功能描述:4 CHANNEL(S), 5 MHZ, DMA CONTROLLER, PQCC44 |

| MSM82C37B-5RS | 制造商:OK International 功能描述:4 CHANNEL(S), 5 MHz, DMA CONTROLLER, PDIP40 |

| MSM82C37B-5VJS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:PROGRAMMABLE DMA CONTROLLER |

| MSM82C43 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:INPUT/OUTPUT PORT EXPANDER |

| MSM82C51A-2GS | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。