- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69040 > MSM7730 (OKI ELECTRIC INDUSTRY CO LTD) 1 CHANNEL(S), 2M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 PDF資料下載

參數(shù)資料

| 型號: | MSM7730 |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), 2M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, 0.50 PITCH, PLASTIC, LQFP-144 |

| 文件頁數(shù): | 5/20頁 |

| 文件大小: | 179K |

| 代理商: | MSM7730 |

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– s MSM7730 s

11

Oki Semiconductor

PIN DESCRIPTIONS

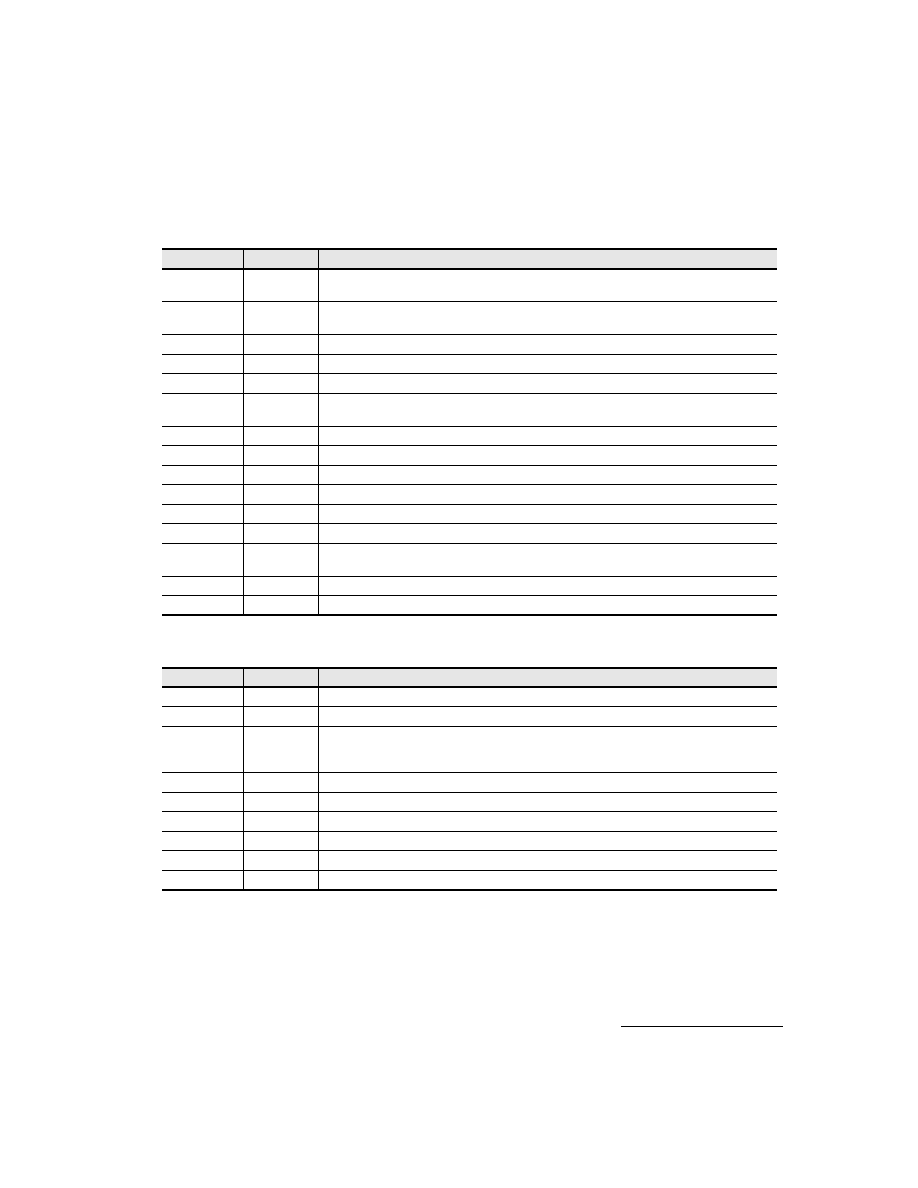

Host Interface Signal Descriptions (PCI and ISA)

Pin Name

Direction

Description

HPACKN

Output

This signal is asserted when the card is selected and can respond to an I/O read cycle at the address on the

address bus.

HIOIS16N

Output

This signal is asserted whenever the access on A[8:0] corresponds to an I/O location which is capable of a 16-

bit access.

HIOWRN

Input

Indicates an I/O write cycle.

HIORDN

Input

Indicates an I/O read cycle.

HIREQN

Output

Active low interrupt request and ready/busy indicator prior to I/O card pin replacement.

HOEN

Input

Output enable signal asserted during memory read operations. Assertion of this signal causes memory data to

be driven onto HD[15:0].

HREGN

Input

Assertion of this signal indicates an access to either attribute memory or I/O space.

HA[8:0]

Input

Least significant 9 bits of the PC-card address bus. All other address bits are ignored.

HCEN[2:1]

Input

Active low card enable signals. HCEN[1] selects even numbered bytes. HCEN[2] selects odd numbered bytes.

HD[15:0]

Bidirectional

Bidirectional data bus. Even numbered bytes appear on HD[7:0]. Odd numbered bytes appear on HD[15:8].

HRST

Input

Active high reset input.

HWAITN

Output

Active low wait output. This signal is asserted if an access is requested that cannot complete immediately.

HWEN

Input

Active low memory write enable input. Indicates a write to either attribute memory or common memory as

determined by the state of the HREGN signal.

HCE1N

Input

Assertion of this signal indicates that a DMA transfer is in progress.

HCE2N

Output

Indicates the ISA shared interrupt status.

Processor Interface Signal Descriptions (V30HL, V53A, and 80C186)

Pin Name

Direction

Description

PD[17:0]

Bidirectional

Bidirectional multiplexed address/data bus driven during the T1 clock state. PD[17:16] are inputs only.

PST[2:0]

Input

Bus status code that indicates the current cycle type. These inputs must be held HIGH when reset is asserted.

PCLK/PCLKOUT

Input/Output

Clock output of the MSM7730 to which all bus interface signals are synchronized. Frequency is 16 MHz during

normal operation but is reduced when in hibernate mode. These two pins must be connected together for

proper operation.

PINTN

Output

This signal is generated by the host and processor interrupt module.

PCSN

Input

Processor chip select.

PREADYN

Output

Active high ready indication from the MSM7730.

PRESETN

Output

This signal is controlled by the host and is asserted based on the state of the PRSTN bit in the H_CTL register.

PUBEN

Input

Upper byte enable. Indicates that a byte of data is to be transferred on PD[15:8].

PREAD

Input

Indicates a read cycle when HIGH, and a write cycle when LOW.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM80C86A-10GS | 16-BIT, 10 MHz, MICROPROCESSOR, PQFP56 |

| MSM80C86A-2GS | 16-BIT, 8 MHz, MICROPROCESSOR, PQFP56 |

| MSM80C86ARS | 16-BIT, 5 MHz, MICROPROCESSOR, PDIP40 |

| MSM80C86AJS | 16-BIT, 5 MHz, MICROPROCESSOR, PQCC44 |

| MSM80C86A-2JS | 16-BIT, 8 MHz, MICROPROCESSOR, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM7731 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Dual Echo Canceler & Noise Canceler with Dual Codec for Hands-Free |

| MSM7731-01 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Multifunction PCM CODEC (Voice Signal Processor) |

| MSM7731-02 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:Dual Echo Canceler & Noise Canceler with Dual Codec for Hands-Free |

| MSM7731-02GAZ020 | 制造商:ROHM Semiconductor 功能描述: |

| MSM7731-02GAZ03A | 制造商:ROHM Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。