- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378678 > MSM548332 (OKI SEMICONDUCTOR CO., LTD.) 278,400-Word×12-Bit Field Memory(278,400字×12位場存儲器) PDF資料下載

參數(shù)資料

| 型號: | MSM548332 |

| 廠商: | OKI SEMICONDUCTOR CO., LTD. |

| 英文描述: | 278,400-Word×12-Bit Field Memory(278,400字×12位場存儲器) |

| 中文描述: | 27.84萬詞× 12位場存儲器(278400字× 12位場存儲器) |

| 文件頁數(shù): | 8/23頁 |

| 文件大小: | 245K |

| 代理商: | MSM548332 |

Semiconductor

MSM548332

8/23

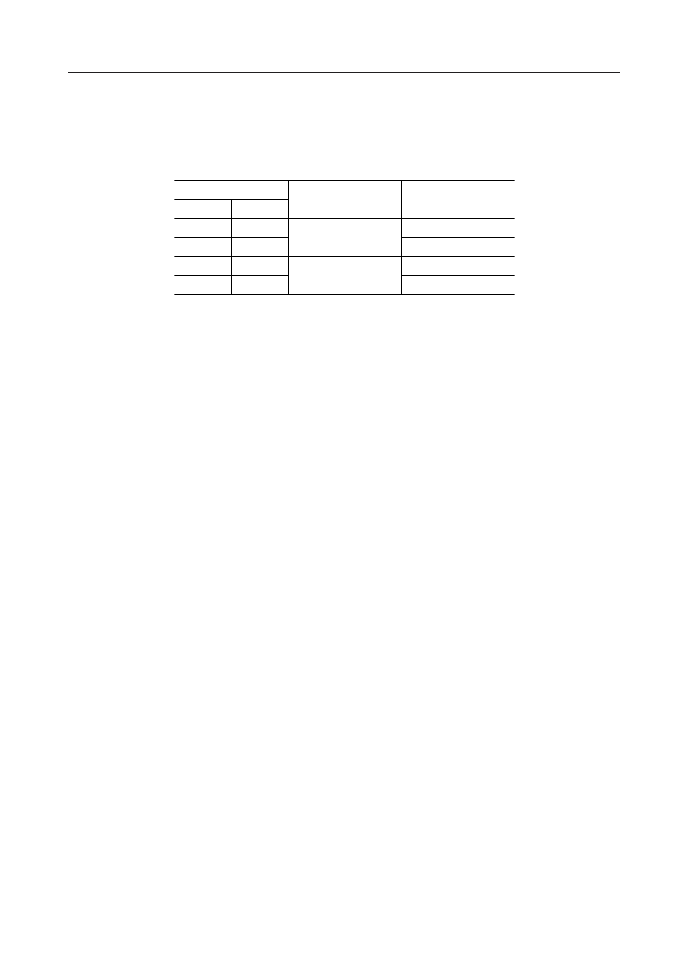

2. Read address pointer increment operation

The read address pointer is incremented synchronized with RCLK when OE level is high.

RE

H

H

L

L

OE

H

L

H

L

RCLK Rise

Internal Read

Address Pointer

Data Output

Incremented

Outputted

Hi-Z

Outputted

Hi-Z

Stopped

Relationship between the RE and OE input levels,

Read Address pointer, and data output status

When each read address pointer reaches the last address of a line, it stops at the last address

and no address increment occurs.

Initial Address Setting (Write/Read Independent)

Any read operations are prohibited in the read initial address set period. Similarly, any write

operations are prohibited in the write initial address set period. Note that read initial address set and

write initial address set can occur independently. Similarly, read access can be achieved independently

from write initial address set period and write access can be achieved independently from read initial

address set cycles.

1. Write address setting

WADE/RX enables initial read address inputs. When WADE/RX is high, 9 bits of serial X

address (or line address) are input from WXAD.

The operations above enable selection of specific lines randomly and enables the start of serial

write access synchronized with write clock WCLK. Address for each line must be input

between each line access. In other words, MSM548332's write is achieved in a "line by line"

manner. Any write operations are prohibited in the initial write address set periods.

Serial write input enable time t

SWE

must be kept for starting a serial write just after the initial

write address set period.

2. Read address setting

RADE/RX enables initial read address inputs.

When RADE/RX is high, 9 bits of serial X address (or line address) are input from RXAD.

The operations above enable selection of specific lines randomly and enables the start of serial

read access synchronized with read clocks, RCLK. Address for each line must be input

between each line access. In other words, MSM548332's read operation is achieved in "line by

line" manner.

Any read operations are prohibited in the initial read address set periods. Serial read

operations are prohibited while RADE/RX is high. Serial read port enable time t

SRE

must be

kept for starting a serial read just after the initial read address set period.

Initial Address Reset Modes (Write/Read Independent)

The initial address reset modes replace complicated read or write initial address settings with simple

reset cycles. Initial address reset modes are selected by RR high during read and WR/TR high during

write. As in normal read or write address settings, any read operations are prohibited in the read

address reset cycles. Similarly, any write operations are prohibited in the initial write address reset

cycles. Note that read initial address reset and write initial address reset can occur independently.

Similarly, read access can be achieved independently from write initial address reset cycles and write

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSM54V32126A | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

| MSM54V32126A-45GS-K | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

| MSM54V32126A-45TS-K | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

| MSM54V32126A-50GS-K | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

| MSM54V32126A-50TS-K | 131,072-Word X 32-Bit DYNAMIC RAM : FAST PAGE MODE TYPE WITH EDO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSM54V12222A-30TS-K | 制造商:OKI Semiconductor 功能描述:FIELD/FRAME/LINE MEMORY, 44 Pin, Plastic, TSOP |

| MSM54V12222B-25JDR17 | 制造商:ROHM Semiconductor 功能描述: |

| MSM54V12222B-25JSDR1 | 制造商:ROHM Semiconductor 功能描述: |

| MSM54V12222B-25T3-K7 | 制造商:ROHM Semiconductor 功能描述: |

| MSM54V12222B-25T3R17 | 制造商:ROHM Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。