- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69036 > MPC5602PEFMLL (FREESCALE SEMICONDUCTOR INC) MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | MPC5602PEFMLL |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, MS-026BED, LQFP-100 |

| 文件頁數(shù): | 56/72頁 |

| 文件大?。?/td> | 661K |

| 代理商: | MPC5602PEFMLL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

MPC560xP Datasheet Data Sheet, Rev. 1

Preliminary—Subject to Change Without Notice

Freescale Semiconductor

6

2

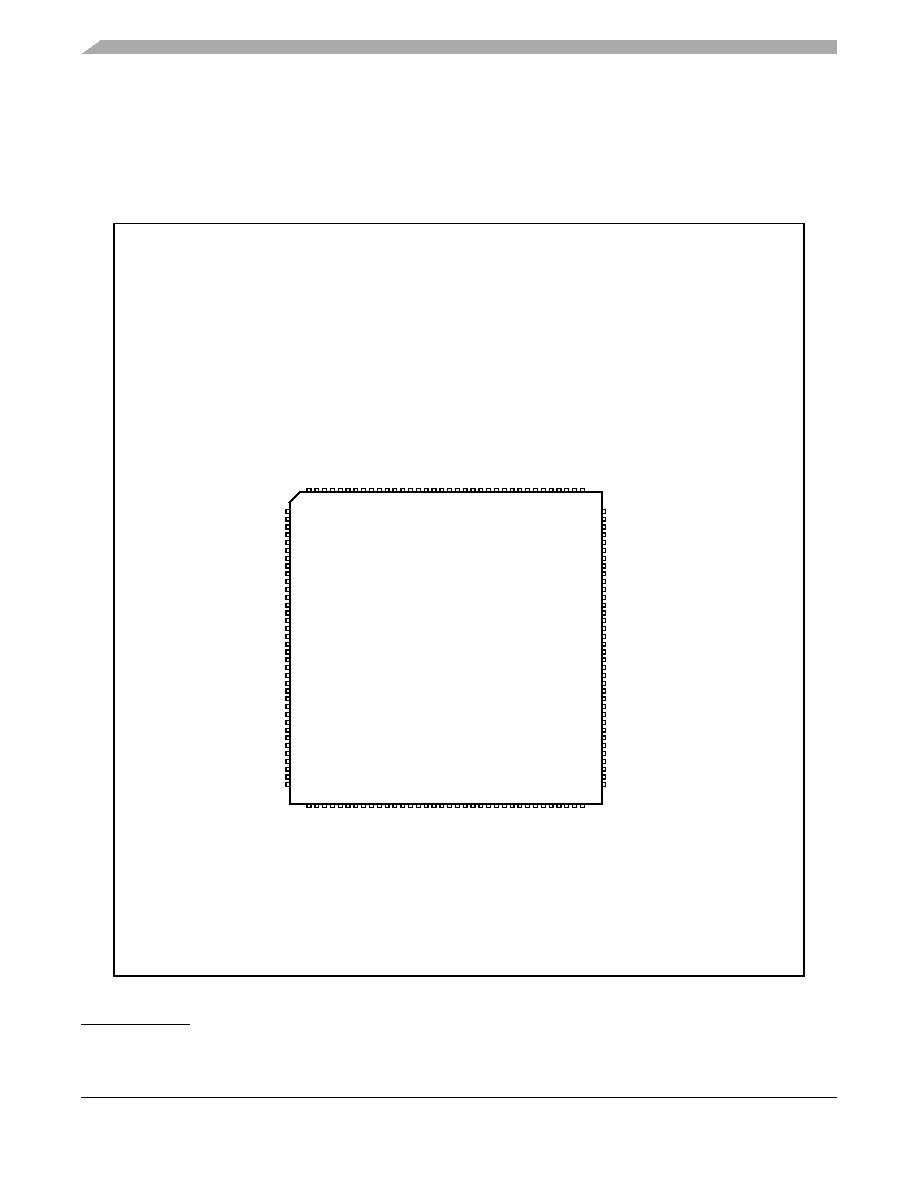

Package Pinouts and Signal Descriptions

2.1

Package Pinouts

The LQFP pinouts are shown in the following figures.

Figure 2. LQFP 144-pin Configuration (top view)1

1. Availability of port pin alternate functions depends on product selection

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

14

4

14

3

14

2

14

1

14

0

13

9

13

8

13

7

13

6

13

5

13

4

13

3

13

2

13

1

13

0

12

9

12

8

12

7

12

6

12

5

12

4

12

3

12

2

12

1

12

0

11

9

11

8

11

7

11

6

11

5

11

4

11

3

11

2

11

1

11

0

10

9

NMI

dspi1 SCK/A[6]

flexray0 CA RX/etimer1 ETC[2]/ctu0 EXT TRG/D[1]

nexus0 MDO[3]/F[4]

nexus0 MDO[2]/F[5]

VDD_HV_IO0

VSS_HV_IO0

nexus0 MDO[1]/F[6]

nexus0 MDO 0

dspi1 SOUT/A[7]

sscm DEBUG[4]/dspi0 CS0/flexpwm0 X[1]/C[4]

dspi1 SIN/A[8]

sscm DEBUG[5]/dspi0 SCK/flexpwm0 FAULT[3]/C[5]

dspi1 CS0/etimer1 ETC[5]/dspi0 CS7/A[5]

sscm DEBUG[7]/dspi0 SIN/flexpwm0 A[1]/C[7]

dspi0 CS1/etimer1 ETC[4]/lin1 TXD/C[3]

VSS_LV_COR0

VDD_LV_COR0

nexus0 MCKO/F[7]

nexus0 MSEO1/F[8]

VDD_HV_IO1

VSS_HV_IO1

nexus0 MSEO0/F[9]

nexus0 EVTO/F[10]

nexus0 EVTI/F[11]

flexpwm0 X[0]/lin1 TXD/D[9]

VDD_HV_OSC

VSS_HV_OSC

XTAL

EXTAL

RESET_B

dspi1 CS2/flexpwm0 FAULT[3]/dspi0 CS5/D[8]

dspi0 CS3/fcu0 F[0]/dspi3 SOUT/D[5]

dspi0 CS2/dspi3 SCK/flexpwm0 FAULT[1]/D[6]

VSS_LV_PLL

VDD_LV_PLL

A[4]/etimer1 ETC[0]/dspi2 CS1/etimer0 ETC[4]

VPP TEST

F[12]/etimer1 ETC[3]

D[14]/flexpwm0 B[1]/dspi3 CS3/dspi3 SIN

G[3]/flexpwm0 A[2]

C[14]/etimer1 ETC[2]/ctu0 EXT TGR

G[2]/flexpwm0 X[2]

C[13]/etimer1 ETC[1]/ctu0 EXT IN/flexpwm0 ext. sync

G[4]/flexpwm0 B[2]

D[12]/flexpwm0 X[1]/lin1 RXD

G[6]/flexpwm0 A[3]

VDD_HV_FL

VSS_HV_FL

D[13]/flexpwm0 A[1]/dspi3 CS2/dspi3 SOUT

VSS_LV_COR1

VDD_LV_COR1

A[3]/etimer0 ETC[3]/dspi2 CS0/flexpwm0 B[3]

VDD_HV_IO2

VSS_HV_IO2

B[4]/jtag0 TDO

jtag0 TCK

jtag0 TMS

B[5]/jtag0 TDI

G[5]/flexpwm0 X[3]

A[2]/etimer0 ETC[2]/dspi2 SIN/flexpwm0 A[3]

G[7]/flexpwm0 B[3]

C[12]/etimer0 ETC[5]/dspi2 CS3/dspi3 CS1

G[8]/flexpwm0 FAULT[0]

C[11]/etimer0 ETC[4]/dspi2 CS2/dspi3 CS0

G[9]/flexpwm0 FAULT[1]

D[11]/flexpwm0 B[0]/dspi3 CS1/dspi3 SCK

G[10]/flexpwm0 FAULT[2]

D[10]/flexpwm0 A[0]/dspi3 CS0

G[11]/flexpwm0 FAULT[3]

A[1]/etimer0 ETC[1]/dspi2 SOUT/fcu0 F[1]/DEBUG[7]

A[0]/etimer0 ETC[0]/dspi2 SCK/fcu0 F[0]

dspi

1

CS

3

/fc

u

0

F[

1]

/dspi

3

SI

N/

d

s

pi

0

CS

4

/D[7

]

fc

u

0

F[

0]

/G[0

]

adc0

A

N

[4

]/

E[

1]

adc0

AN

[6]

/E[

3]

adc0

A

N

[2

]/

C[1

]

adc0

A

N

[7

]/

E[

4]

adc0

AN

[0

]/

lin

0

RX

D/

B[7

]

adc0

A

N

[8

]/

E[

5]

adc0

A

N

[3

]/

C[2

]

adc0

A

N

[9

]/

E[

6]

adc0

AN

[1

]/

et

im

er

0

ET

C[

5

]/

B[8

]

adc0

AN

[10]

/E[

7]

adc0

AN

[5]

/E[

2]

V

DD

_

H

V

_

AD0

V

SS

_

H

V_

A

D

0

adc0-

adc1

AN

[11]

/B[9

]

a

d

c0-

adc1

A

N

[12]

/B[

1

0

]

a

d

c0-

adc1

A

N

[13]

/B[

1

]

a

d

c0-

adc1

A

N

[14]

/B[

1

2

]

V

DD

_

H

V

_

AD1

V

SS

_

H

V_

A

D

1

adc1

A

N

[4

]/

D[

1

5

]

adc1

A

N

[6

]/

E[

8]

adc1

A

N

[0

]/

lin

1

RX

D/

B[

1

3

]

adc1

A

N

[7

]/

E[

9]

adc1

A

N

[2

]/

B[

1

5

]

adc1

AN

[8]

/E[

10

]

ad

c

1

A

N

[1

]/

et

im

er

0

ET

C

[4

]/

B[

1

4

]

adc1

A

N

[9

]/

E[

11

]

adc1

A

N

[3

]/

C[0

]

adc1

AN

[10]

/E[

12

]

adc1

A

N

[5

]/

E[

0]

BC

TRL

V

DD

_

LV_

RE

GC

OR

V

SS

_L

V_RE

GC

OR

V

DD_HV_REG

A

[15]

/saf

e

ty

por

t0

RXD

/et

im

e

r1

ETC

[5]

A

[14]

/saf

e

ty

por

t0

TXD

/et

im

er

1

ETC

[4]

C[

6

]/

dspi

0

SO

UT

/fl

e

x

p

w

m0

B[1

]/

sscm

DE

BU

G[6

]

G[

1

]/

fc

u

0

F[

1]

D[

2

]/

fl

e

x

ra

y

0

CB

R

X

/et

im

er

1

ET

C

[3

]/

fl

e

x

p

w

m0

X[3

]

F[

3]

/fl

e

x

ra

y

0

DB

G3

/dspi

3

CS

0

B[

6

]/C

L

K

OU

T

/dspi

2

CS

2

F[

2]

/fl

e

x

ra

y

0

DB

G2

/dspi

3

CS

1

A

[13]

/dspi

2

SI

N

/fl

e

x

p

w

m0

B[

2

]/

fl

e

x

p

w

m

0

FA

U

LT

[0

]

F[

1]

/f

le

x

ra

y0

DB

G1

/dspi

3

CS

2

A[

9

]/

dspi

2

CS

1

/fl

e

x

p

w

m

0

FA

U

LT

[0

]/

fl

e

x

p

w

m

0

B[

3

]

F[

0]

/fl

e

x

ra

y

0

DB

G0

/dspi

3

CS

3

V

SS_L

V

_CO

R

2

V

DD_

LV

_

C

O

R

2

C[

8

]/

dspi

1

CS

1

/fl

e

x

p

w

m

0

FA

U

LT

[2

]/

dspi

0

CS

6

D[

4

]/

fl

e

x

ra

y

0

CB

T

R

E

N

/et

im

er

1

ETC

[5]

/fl

e

x

p

w

m0

B[

3]

D[

3

]/

fl

e

x

ra

y

0

CB

T

X

/et

im

er

1

ET

C[

4]/

fl

e

x

p

w

m0

A[

3

]

V

SS_H

V

_I

O3

V

DD_

HV_

IO3

D[

0

]/

fl

e

x

ra

y

0

CA

T

X

/et

im

er

1

ET

C[

1]/

fl

e

x

p

w

m0

B[

1

]

C

[15]

/fl

e

x

ra

y

0

CA

T

R

E

N

/et

im

e

r1

ETC

[0

]/

fl

e

x

p

w

m0

A[

1]

/ct

u0

EXT

IN

/fl

e

x

p

w

m0

e

x

t.

s

y

n

c

C[

9

]/

dspi

2

CS

3

/fl

e

x

p

w

m

0

FA

U

LT

[2

]/

fl

e

x

p

w

m

0

X[

3

]

A

[12]

/dspi

2

SO

U

T

/fl

e

x

p

w

m0

A[

2]/

fl

e

x

p

w

m0

B[

2]

E[

15]

/dspi

3

SI

N

A

[11]

/dspi

2

SC

K/

fl

e

x

p

w

m0

A[

0

]/

fl

e

x

p

w

m0

A[

2]

E[

14]

/dspi

3

SO

UT

A

[10]

/dspi

2

CS

0

/fl

e

x

p

w

m0

B[

0]

/fl

e

x

p

w

m0

X[

2

]

E[

13]

/dspi

3

SC

K

B[

3

]/

lin

0

RX

D/

sscm

DEB

U

G

[3

]

F[

14]

/li

n

1

TX

D

B[

2

]/

lin

0

TX

D

/sscm

DE

BUG

[2

]

F[

15]

/li

n

1

RX

D

F[

13]

/et

im

e

r1

ETC

[4]

C

[10]

/dspi

2

CS

2

/fl

e

x

p

w

m0

FA

U

LT

[1

]/

fl

e

x

p

w

m0

A[

3

]

B[

1

]/

can0

RXD

/et

im

e

r1

ETC

[3

]/

sscm

DE

BUG

[1

]

B[

0

]/

can0

TXD

/et

im

er

1

ETC

[2]

/s

scm

D

EBU

G[

0]

144 LQFP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC5603PEFMLQ | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP144 |

| MPC5603PEFMLL | 32-BIT, FLASH, 64 MHz, MICROCONTROLLER, PQFP100 |

| MPC603AFE66CB | 32-BIT, 66.67 MHz, RISC PROCESSOR, CQFP240 |

| MPC603AFE66CX | 32-BIT, 66.67 MHz, RISC PROCESSOR, CQFP240 |

| MPC603AFE80CX | 32-BIT, 80 MHz, RISC PROCESSOR, CQFP240 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC5602S | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC5606S Microcontroller Data Sheet |

| MPC5603B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Qorivva MPC560xB/C/D Family |

| MPC5603BEMLL | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC5604B/C Microcontroller Data Sheet |

| MPC5603BEMLLR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC5604B/C Microcontroller Data Sheet |

| MPC5603BEMLQ | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC5604B/C Microcontroller Data Sheet |

發(fā)布緊急采購,3分鐘左右您將得到回復。