- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45337 > MPC5534MVF66 (FREESCALE SEMICONDUCTOR INC) MICROCONTROLLER, PBGA208 PDF資料下載

參數(shù)資料

| 型號(hào): | MPC5534MVF66 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PBGA208 |

| 封裝: | 17 X 17 MM, 1 MM PITCH, PLASTIC, MO-151AAF-1, MAPBGA-208 |

| 文件頁(yè)數(shù): | 4/60頁(yè) |

| 文件大小: | 1055K |

| 代理商: | MPC5534MVF66 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

MPC5534 Microcontroller Data Sheet, Rev. 5

Electrical Characteristics

Freescale Semiconductor

12

3.7.1

Input Value of Pins During POR Dependent on VDD33

When powering up the device, VDD33 must not lag the latest VDDSYN or RESET power pin (VDDEH6) by

more than the VDD33 lag specification listed in Table 6, spec 8. This avoids accidentally selecting the

bypass clock mode because the internal versions of PLLCFG[0:1] and RSTCFG are not powered and

therefore cannot read the default state when POR negates. VDD33 can lag VDDSYN or the RESET power

pin (VDDEH6), but cannot lag both by more than the VDD33 lag specification. This VDD33 lag specification

applies during power up only. VDD33 has no lead or lag requirements when powering down.

3.7.2

Power-Up Sequence (VRC33 Grounded)

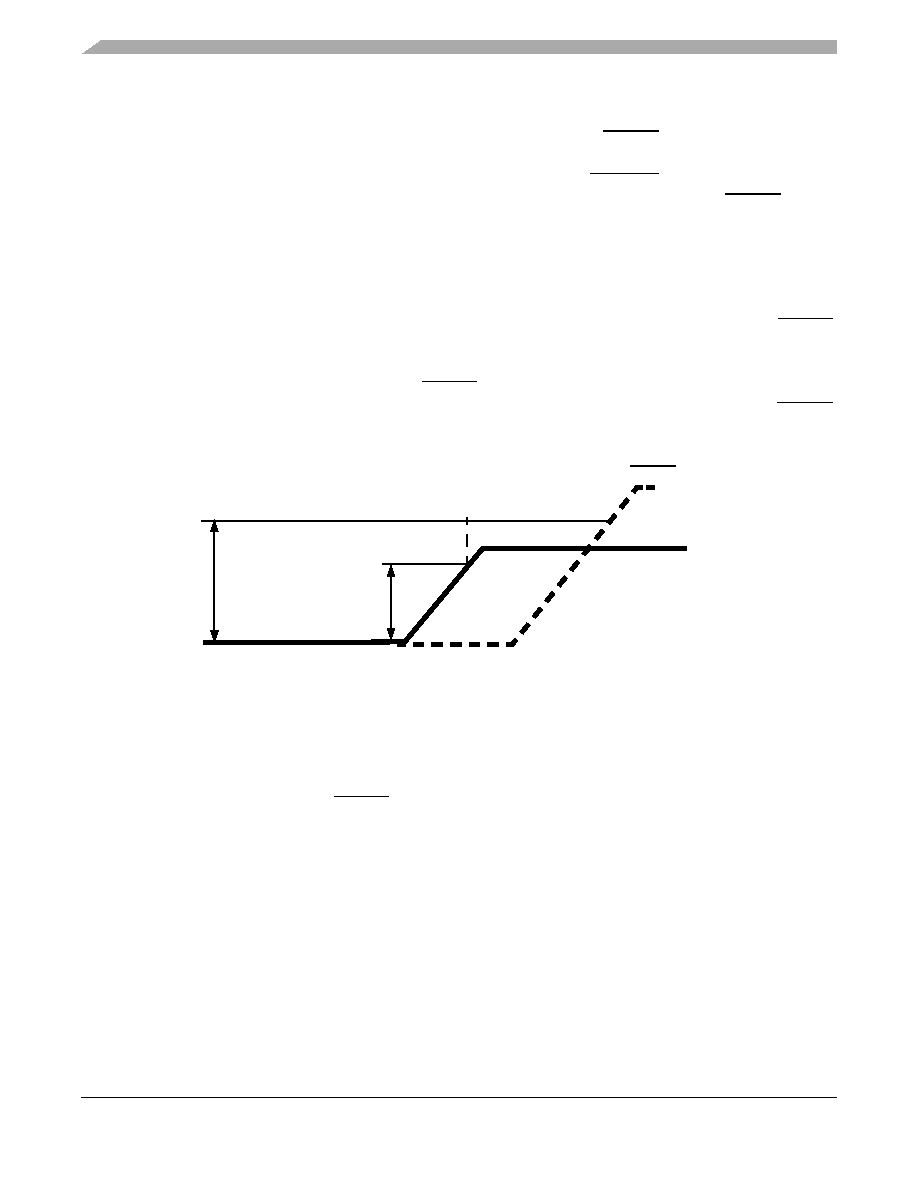

The 1.5 V VDD power supply must rise to 1.35 V before the 3.3 V VDDSYN power supply and the RESET

power supply rises above 2.0 V. This ensures that digital logic in the PLL for the 1.5 V power supply does

not begin to operate below the specified operation range lower limit of 1.35 V. Because the internal 1.5 V

POR is disabled, the internal 3.3 V POR or the RESET power POR must hold the device in reset. Since

they can negate as low as 2.0 V, VDD must be within specification before the 3.3 V POR and the RESET

POR negate.

Figure 2. Power-Up Sequence (VRC33 Grounded)

3.7.3

Power-Down Sequence (VRC33 Grounded)

The only requirement for the power-down sequence with VRC33 grounded is if VDD decreases to less than

its operating range, VDDSYN or the RESET power must decrease to less than 2.0 V before the VDD power

increases to its operating range. This ensures that the digital 1.5 V logic, which is reset only by an ORed

POR and can cause the 1.5 V supply to decrease less than its specification value, resets correctly. See

Table 6, footnote 1.

VDDSYN and RESET Power

VDD

2.0 V

1.35 V

VDD must reach 1.35 V before VDDSYN and the RESET power reach 2.0 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC5534MZQ40 | MICROCONTROLLER, PBGA324 |

| MPC5534MZQ66 | MICROCONTROLLER, PBGA324 |

| MPC5534MZQ80 | FLASH, 80 MHz, MICROCONTROLLER, PBGA324 |

| MPC5534MVF40 | MICROCONTROLLER, PBGA208 |

| MPC5553MVR132 | 32-BIT, FLASH, 132 MHz, MICROCONTROLLER, PBGA416 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC5534MVF66R2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5534MVF80 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5534MVF80R2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5534MVM40 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

| MPC5534MVM40R2 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。