- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25635 > MD80C52EXXX-20SB (ATMEL CORP) 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號(hào): | MD80C52EXXX-20SB |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| 封裝: | 0.600 INCH, CERAMIC, DIP-40 |

| 文件頁(yè)數(shù): | 156/198頁(yè) |

| 文件大?。?/td> | 4822K |

| 代理商: | MD80C52EXXX-20SB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)當(dāng)前第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)

60

8111C–MCU Wireless–09/09

AT86RF231

Note that this feature can be used in all scenarios, independent of other configurations. How-

ever, shorter acknowledgment timing is especially useful when using High Data Rate Modes to

increase battery lifetime and to improve the overall data throughput; refer to Section 11.3 “High

7.2.3.4

RX_AACK_NOCLK - RX_AACK_ON without CLKM

If the AT86RF231 is listening for an incoming frame and the microcontroller is not running an

application, the microcontroller can be powered down to decrease the total system power con-

sumption. This special power-down scenario for systems running in clock synchronous mode

(see Section 6. “Microcontroller Interface” on page 16) is supported by the AT86RF231 using the

state RX_AACK_ON_NOCLK. The radio transceiver functionality in this state is based on that in

state RX_AACK_ON with pin 17 (CLKM) disabled.

The RX_AACK_NOCLK state is entered from RX_AACK_ON by a rising edge at pin 11

(SLP_TR). The return to RX_AACK_ON state results either from a successful frame reception or

a falling edge on pin SLP_TR.

The CLKM pin is disabled 35 clock cycles after the rising edge at SLP_TR pin. This allows the

microcontroller to complete its power-down sequence. This is not valid for clock rates 250 kHz

and 62.5 kHz, where the main clock at pin 17 (CLKM) is switched off immediately.

In case of the reception of a valid frame, IRQ_3 (TRX_END) is issued and pin 17 (CLKM) is

turned on. A timing diagram is shown in Figure 6-16 on page 28. A received frame is considered

valid if it passes address filtering and has a correct FCS. If an ACK was requested the radio

transceiver enters BUSY_RX_AACK state and follows the procedure described in Section 7.2.3

After the transaction has been completed, the radio transceiver reenters the RX_AACK_ON

state.

The radio transceiver reenters the RX_AACK_ON_NOCLK state only, when the next rising edge

at SLP_TR pin occurs.

It is not recommended to operate the receiver in state RX_AACK_NOCLK with register bit

SLOTTED_OPERATION (register 0x2C, XAH_XTRL_0) set, refer to “Register Description -

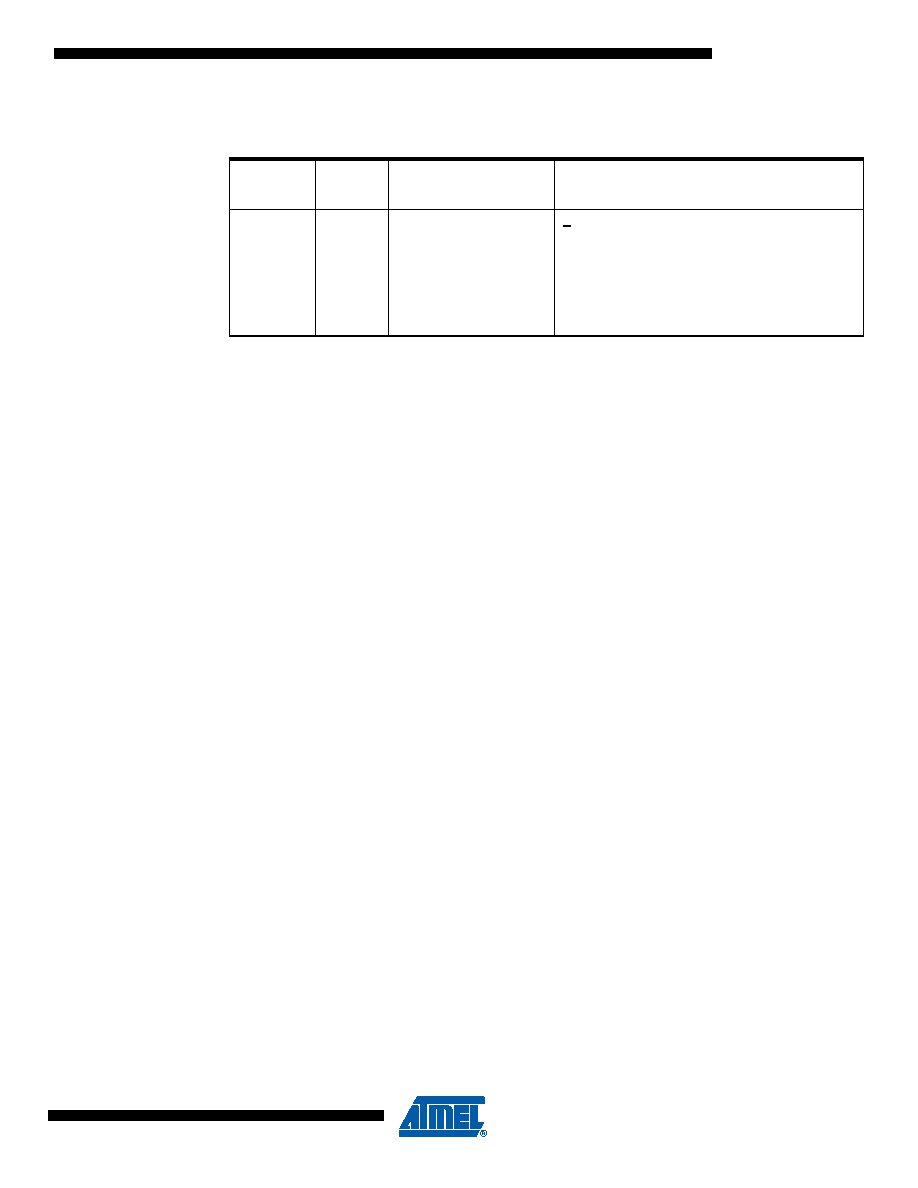

Table 7-11.

Overview of RX_AACK Configuration Bits

Register

Register Name

Description

Address

Bit

0x17

2

AACK_ACK_TIME

0: Standard compliant acknowledgement timing

of 12 symbol periods. In slotted acknowledge-

ment operation mode, the acknowledgment

frame transmission can be triggered 6 symbol

periods after reception of the frame earliest.

1: Reduced acknowledgment timing of 2 symbol

periods (32 s).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C32E-36SC | 8-BIT, 36 MHz, MICROCONTROLLER, CQFP44 |

| MR80C52XXX-20:R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C32E-30/883 | 8-BIT, 30 MHz, MICROCONTROLLER, CQFP44 |

| MR80C52CXXX-16/883R | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQCC44 |

| MR80C52TXXX-16SB | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MD80C86 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C862 | 制造商:Intel 功能描述:PROCESSOR:MICRO-PROCESSOR |

| MD80C86-2 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C86-2/883 | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 8MHZ 40CDIP - Rail/Tube 制造商:Rochester Electronics LLC 功能描述:CPU 16BILT 5V CMOS 8MHZ 40CDIP - Bulk |

| MD80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 8MHZ 40CDIP - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。