- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98013 > MCZ33781EK (FREESCALE SEMICONDUCTOR INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO32 PDF資料下載

參數(shù)資料

| 型號: | MCZ33781EK |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO32 |

| 封裝: | 0.65 MM, LEAD FREE, SOIC-32 |

| 文件頁數(shù): | 13/44頁 |

| 文件大小: | 940K |

| 代理商: | MCZ33781EK |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

Analog Integrated Circuit Device Data

20

Freescale Semiconductor

33781

FUNCTIONAL DESCRIPTIONS

FUNCTIONAL INTERNAL BLOCK DESCRIPTION

PSEUDO BUS SWITCHES

Pseudo Bus Switches are provided on the Channel 0 bus.

They allow one channel to communicate via two external bus

wire sets (D0H/D0L and DPH/DPL). There is a pseudo bus

switch on both the bus high and bus low driver. Upon device

reset the bus switches are open. This allows the master to

initialize devices on D0H/D0L. After all of these slaves are

initialized, the pseudo bus switches can be closed, allowing

the devices on DPH/DPL to be initialized.

The Pseudo Bus Switches can only be commanded closed

by the BSWH and BSWL bits in the D0EN register. These bits

can also open the switch at any time.

The Pseudo Bus Switches have independent thermal

shutdown protection. Once the thermal shutdown point is

reached, the bus switch is opened (becoming high-

impedance) and the BSWH and/or BSWL bit is cleared in the

channel 0 DEN register. If this occurs, the Pseudo Bus

Switches can only be closed again by setting the BSWH and/

or BSWL bit to a 1 with a write command to the channel 0

DEN register.

SPREAD SPECTRUM

The dominant source of radiated electromagnetic

interference (EMI) from the DBUS bus is due to the regular

periodic frequency of the data bits. At a steady bit rate, the

time period for each bit is the same, which results in a steady

fundamental frequency plus harmonics. This results in

undesired signals appearing at multiples of the frequency

that can be strong enough to interfere with a desired signal.

A significant decrease in radiated EMI can be achieved by

randomly changing the duration of each bit. This can

significantly reduce the amplitude by having the signal spend

a much smaller percentage of time at any specific frequency.

The signal strength of the fundamental and harmonics are

reduced directly by the percentage of time it spends on a

specific frequency.

A circuit to do this is included in this IC, and can perform

the spreading of the signal independently for each channel,

while generating the bit clock timing for the channel. This is

done in the Spread Spectrum (SS) Block Diagram shown in

To implement the channel bit clock a common 64MHz

clock is created from the on board 4MHz oscillator using a

digital PLL. Multiples of this clock period (15.625 nsec) are

used to select the minimum channel bit time. The Spread

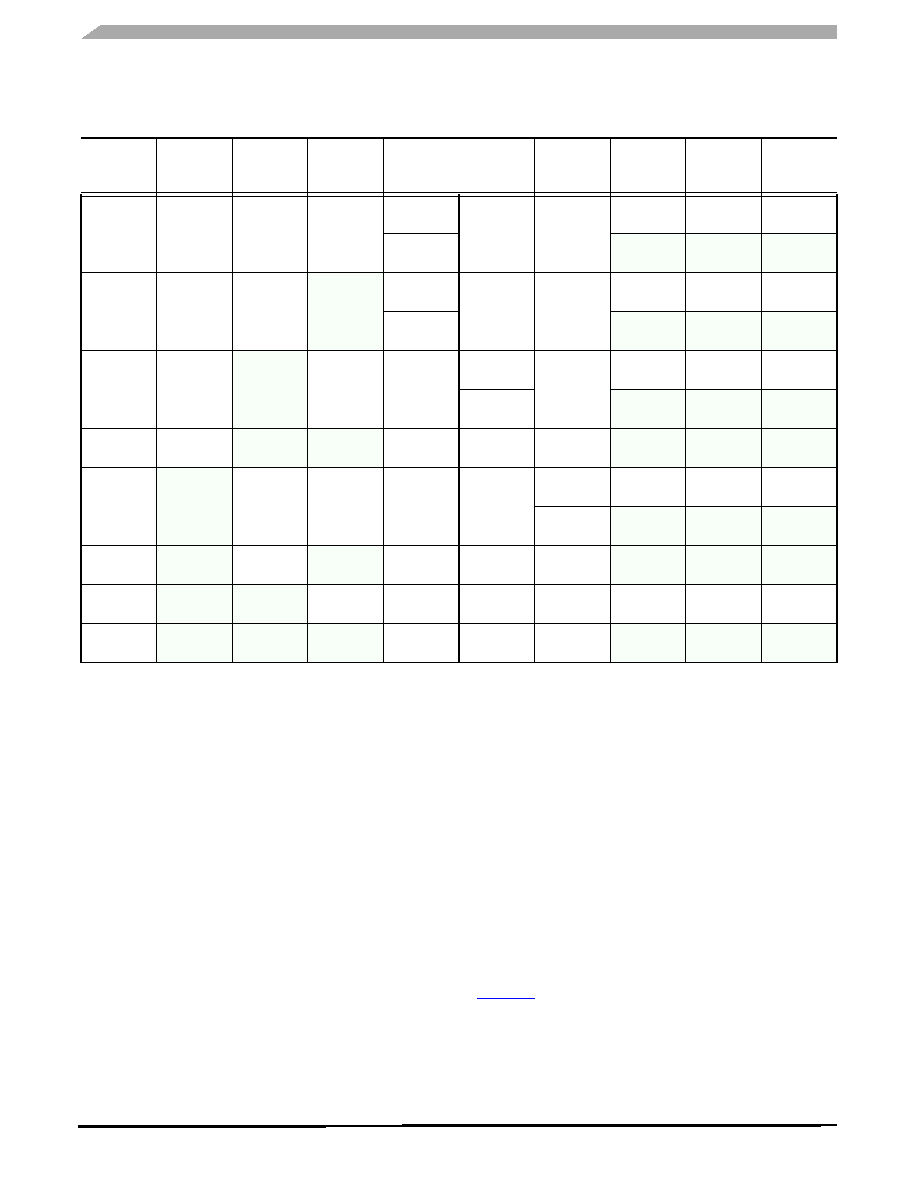

Table 7. Receiver Decision Logic

Bus Pin

Conditions

Receiver

High 6 ± 1

mA

Receiver

Low 6 ± 1

mA

Receiver

Sum 12 ±

6mA

High and

Low XOR

(bit/bit)

High and

Sum XOR

(bit/bit)

Low and

Sum XOR

(bit/bit)

ER Bit

SPI0

DnRnxData

SPI1

DnRnxData

Normal

CRC Ok

H*L Ok

N/A

0

Receiver

High

Receiver

Low

H*L Not OK

1

Receiver

High

Receiver

Low

Out of Spec

CRC Ok

Bad CRC

H*L Ok

N/A

0

Receiver

High

Receiver

Low

H*L Not OK

1

Receiver

High

Receiver

Low

Fault

CRC Ok

Bad CRC

CRC Ok

N/A

H*S Ok

N/A

0

Receiver

High

Receiver

Sum1

H*S Not OK

1

Receiver

High

Receiver

Low

Fault L

CRC Ok

Bad CRC

N/A

1

Receiver

High

Receiver

Low

Fault

Bad CRC

CRC OK

N/A

L*S Ok

0

Receiver

Sum0

Receiver

Low

L*S Not OK

1

Receiver

High

Receiver

Low

Fault H

Bad CRC

CRC Ok

Bad CRC

N/A

1

Receiver

High

Receiver

Low

Common

Mode Noise

Bad CRC

CRC Ok

N/A

0

Receiver

Sum0

Receiver

Sum1

Fault

Bad CRC

N/A

1

Receiver

High

Receiver

Low

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MD1802FH | 10 A, 700 V, NPN, Si, POWER TRANSISTOR, TO-220AB |

| MD1802FX | 10 A, 700 V, NPN, Si, POWER TRANSISTOR |

| MD1803DFH | 10 A, 700 V, NPN, Si, POWER TRANSISTOR, TO-220AB |

| MD2001FX | 12 A, 700 V, NPN, Si, POWER TRANSISTOR |

| MD2103DFX | 6 A, 700 V, NPN, Si, POWER TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCZ33781EKR2 | 功能描述:輸入/輸出控制器接口集成電路 DBUS2 MASTER STND RoHS:否 制造商:Silicon Labs 產(chǎn)品: 輸入/輸出端數(shù)量: 工作電源電壓: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-64 封裝:Tray |

| MCZ33784EF | 功能描述:加速計(jì) - 板上安裝 DBUS2 SENSOR INTERFACE RoHS:否 制造商:Murata 傳感軸:Double 加速:12 g 靈敏度: 封裝 / 箱體: 輸出類型:Analog 數(shù)字輸出 - 位數(shù):11 bit 電源電壓-最大:5.25 V 電源電壓-最小:4.75 V 電源電流:4 mA 最大工作溫度:+ 125 C 最小工作溫度:- 40 C |

| MCZ33784EF/R2- | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:DSI 2.02 Sensor Interface |

| MCZ33784EFR2 | 功能描述:加速計(jì) - 板上安裝 DBUS2 SENSOR INTERFACE RoHS:否 制造商:Murata 傳感軸:Double 加速:12 g 靈敏度: 封裝 / 箱體: 輸出類型:Analog 數(shù)字輸出 - 位數(shù):11 bit 電源電壓-最大:5.25 V 電源電壓-最小:4.75 V 電源電流:4 mA 最大工作溫度:+ 125 C 最小工作溫度:- 40 C |

| MCZ33789AE | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Airbag ASSP RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。