- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69032 > MCV14AI/SL 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 PDF資料下載

參數(shù)資料

| 型號: | MCV14AI/SL |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| 封裝: | 3.90 MM, PLASTIC, SOIC-4 |

| 文件頁數(shù): | 22/84頁 |

| 文件大?。?/td> | 1007K |

| 代理商: | MCV14AI/SL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

2009 Microchip Technology Inc.

Preliminary

DS41338B-page 27

MCV14A

5.5

I/O Programming Considerations

5.5.1

BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed

by write operations. The BCF and BSF instructions, for

example, read the entire port into the CPU, execute the

bit operation and rewrite the result. Caution must be

used when these instructions are applied to a port

where one or more pins are used as input/outputs. For

example, a BSF operation on bit 5 of PORTB will cause

all eight bits of PORTB to be read into the CPU, bit 5 to

be set and the PORTB value to be written to the output

latches. If another bit of PORTB is used as a bidirec-

tional I/O pin (say bit 0) and it is defined as an input at

this time, the input signal present on the pin itself would

be read into the CPU and rewritten to the data latch of

this particular pin, overwriting the previous content. As

long as the pin stays in the Input mode, no problem

occurs. However, if bit 0 is switched into Output mode

later on, the content of the data latch may now be

unknown.

Example 5-1 shows the effect of two sequential

Read-Modify-Write instructions (e.g., BCF, BSF, etc.)

on an I/O port.

A pin actively outputting a high or a low should not be

driven from external devices at the same time in order

to change the level on this pin (“wired OR”, “wired

AND”). The resulting high output currents may damage

the chip.

EXAMPLE 5-1:

READ-MODIFY-WRITE

INSTRUCTIONS ON AN

I/O PORT(e.g., MCV14A)

5.5.2

SUCCESSIVE OPERATIONS ON

I/O PORTS

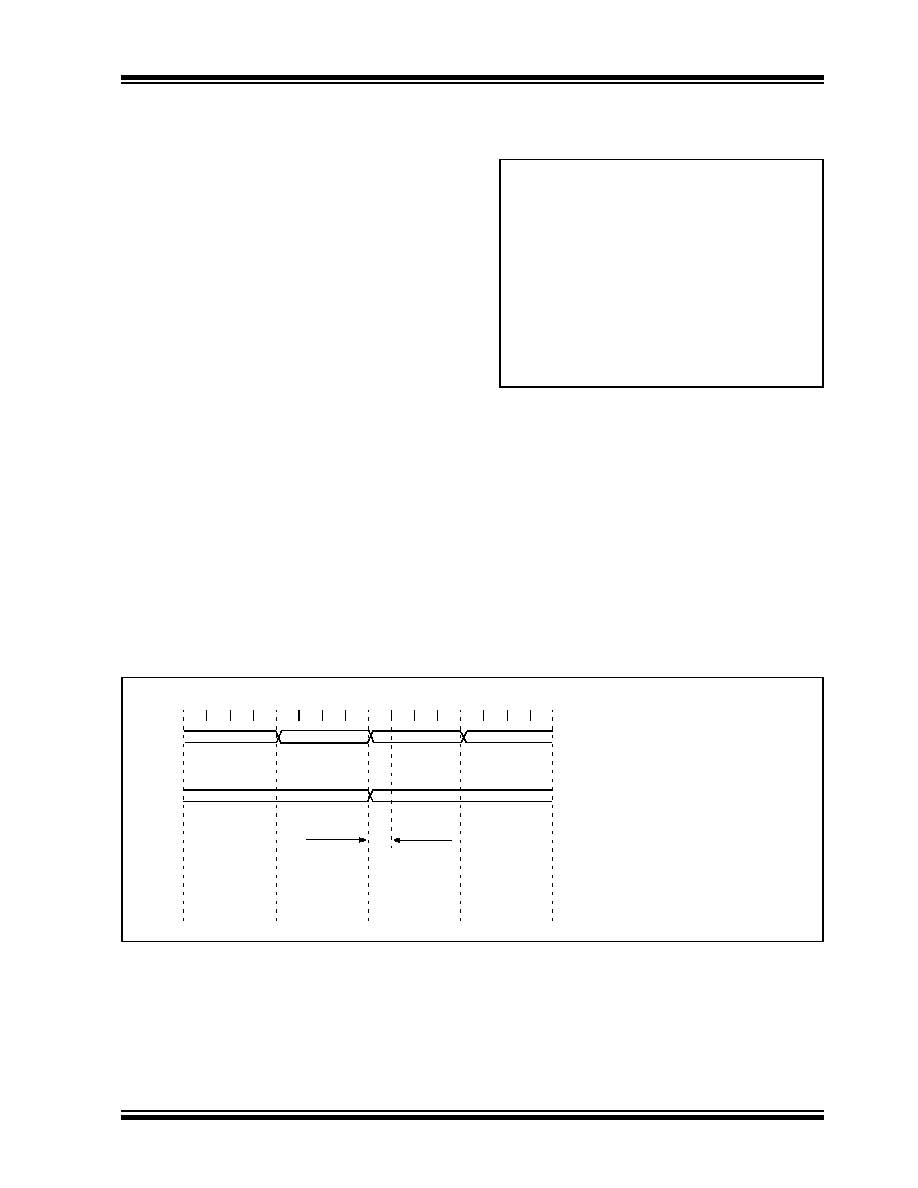

The actual write to an I/O port happens at the end of an

instruction cycle, whereas for reading, the data must be

valid at the beginning of the instruction cycle (Figure 5-2).

Therefore, care must be exercised if a write followed by

a read operation is carried out on the same I/O port. The

sequence of instructions should allow the pin voltage to

stabilize (load dependent) before the next instruction

causes that file to be read into the CPU. Otherwise, the

previous state of that pin may be read into the CPU rather

than the new state. When in doubt, it is better to separate

these instructions with a NOP or another instruction not

accessing this I/O port.

FIGURE 5-2:

SUCCESSIVE I/O OPERATION

;Initial PORTB Settings

;PORTB<5:3> Inputs

;PORTB<2:0> Outputs

;

PORTB latch

PORTB pins

;

----------

BCF

PORTB, 5 ;--01 -ppp

--11 pppp

BCF

PORTB, 4 ;--10 -ppp

--11 pppp

MOVLW

007h;

TRIS

PORTB

;--10 -ppp

--11 pppp

;

Note

1:

The user may have expected the pin values to

be ‘--00 pppp’. The 2nd BCF caused RB5 to

be latched as the pin value (High).

PC

PC + 1

PC + 2

PC + 3

Q1 Q2

Q3 Q4

Q1 Q2 Q3 Q4

Q1

Q2 Q3 Q4

Q1 Q2

Q3 Q4

Instruction

Fetched

RB<5:0>

MOVWF PORTB

NOP

Port pin

sampled here

NOP

MOVF PORTB

, W

Instruction

Executed

MOVWF PORTB

(Write to PORTB)

NOP

MOVF PORTB,W

This example shows a write to PORTB

followed by a read from PORTB.

Data setup time = (0.25 TCY – TPD)

where: TCY = instruction cycle.

TPD = propagation delay

Therefore, at higher clock frequencies, a

write followed by a read may be problematic.

(Read PORTB)

Port pin

written here

相關PDF資料 |

PDF描述 |

|---|---|

| MCV14ATI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| MCV14AI/P | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDIP14 |

| MD8031AHB883B | 8-BIT, 12 MHz, MICROCONTROLLER, CDIP40 |

| MD8255A | 24 I/O, PIA-GENERAL PURPOSE, PDIP40 |

| MD82C52-/883 | 1 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, CDIP28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MCV15/10-GF-381 | 制造商:Phoenix Contact 功能描述:HEADER PCB VERTICAL 3.81MM 10WAY |

| MCV15/2-GF-381 | 制造商:Phoenix Contact 功能描述:HEADER PCB VERTICAL 3.81MM 2WAY |

| MCV15/3-GF-381 | 制造商:Phoenix Contact 功能描述:HEADER PCB VERTICAL 3.81MM 3WAY |

| MCV15/4-GF-381 | 制造商:Phoenix Contact 功能描述:HEADER PCB VERTICAL 3.81MM 4WAY |

| MCV15/5-GF-381 | 制造商:Phoenix Contact 功能描述:HEADER PCB VERTICAL 3.81MM 5WAY |

發(fā)布緊急采購,3分鐘左右您將得到回復。