- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98013 > MCP2510T-E/P 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, PDIP18 PDF資料下載

參數(shù)資料

| 型號: | MCP2510T-E/P |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, PDIP18 |

| 封裝: | 0.300 INCH, PLASTIC, DIP-18 |

| 文件頁數(shù): | 40/76頁 |

| 文件大?。?/td> | 1076K |

| 代理商: | MCP2510T-E/P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

1999 Microchip Technology Inc.

Preliminary

DS21291C-page 45

MCP2510

7.0

INTERRUPTS

The device has eight sources of interrupts. The CANINTE

register contains the individual interrupt enable bits for

each interrupt source. The CANINTF register contains the

corresponding interrupt flag bit for each interrupt source.

When an interrupt occurs the INT pin is driven low by the

MCP2510 and will remain low until the Interrupt is cleared

by the MCU. An Interrupt can not be cleared if the respec-

tive condition still prevails.

It is recommended that the bit modify command be

used to reset flag bits in the CANINTF register rather

than normal write operations. This is to prevent unin-

tentionally changing a flag that changes during the

write command, potentially causing an interrupt to be

missed.

It should be noted that the CANINTF flags are read/

write and an Interrupt can be generated by the MCU

setting any of these bits, provided the associated CAN-

INTE bit is also set.

7.1

Interrupt Code Bits

The source of a pending interrupt is indicated in the

CANSTAT.ICOD (interrupt code) bits as indicated in

Register 9-2. In the event that multiple interrupts occur,

the INT will remain low until all interrupts have been

reset by the MCU, and the CANSTAT.ICOD bits will

reflect the code for the highest priority interrupt that is

currently pending. Interrupts are internally prioritized

such that the lower the ICOD value the higher the inter-

rupt priority. Once the highest priority interrupt condi-

tion has been cleared, the code for the next highest

priority interrupt that is pending (if any) will be reflected

by the ICOD bits (see Table 7-1). Note that only those

interrupt sources that have their associated CANINTE

enable bit set will be reflected in the ICOD bits.

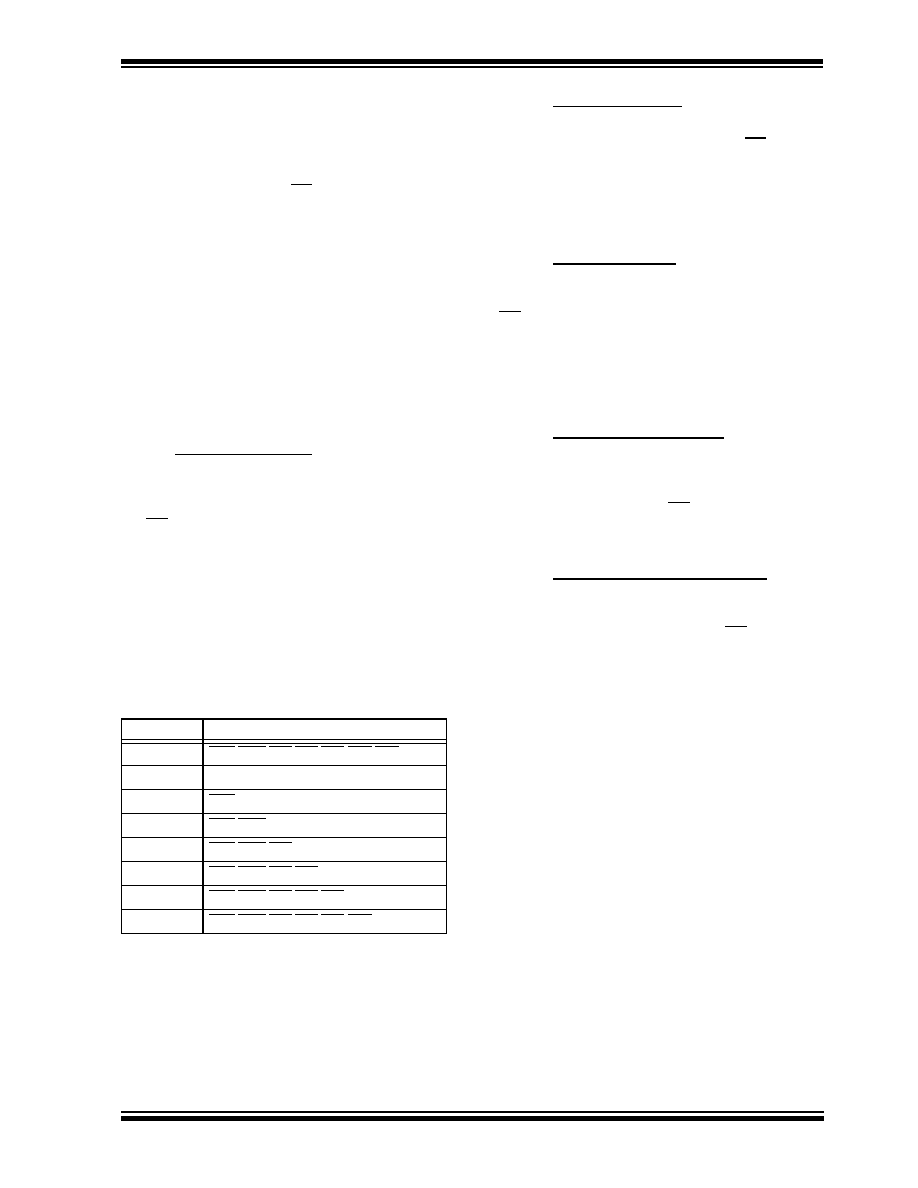

TABLE 7-1:

ICOD<2:0> Decode

7.2

Transmit Interrupt

When the Transmit Interrupt is enabled (CANINTE.TXNIE

= 1) an Interrupt will be generated on the INT pin when

the associated transmit buffer becomes empty and is

ready to be loaded with a new message. The CAN-

INTF.TXNIF bit will be set to indicate the source of the

interrupt. The interrupt is cleared by the MCU resetting

the TXNIF bit to a ‘0’.

7.3

Receive Interrupt

When

the

Receive

Interrupt

is

enabled

(CAN-

INTE.RXNIE = 1) an interrupt will be generated on the

INT pin when a message has been successfully

received and loaded into the associated receive buffer.

This interrupt is activated immediately after receiving the

EOF field. The CANINTF.RXNIF bit will be set to indicate

the source of the interrupt. The interrupt is cleared by the

MCU resetting the RXNIF bit to a ‘0’.

7.4

Message Error Interrupt

When an error occurs during transmission or reception of

a message the message error flag (CANINTF.MERRF)

will be set and, if the CANINTE.MERRE bit is set, an inter-

rupt will be generated on the INT pin. This is intended to

be used to facilitate baud rate determination when used in

conjunction with listen-only mode.

7.5

Bus Activity Wakeup Interrupt

When the MCP2510 is in sleep mode and the bus activ-

ity wakeup interrupt is enabled (CANINTE.WAKIE = 1),

an interrupt will be generated on the INT pin, and the

CANINTF.WAKIF bit will be set when activity is

detected on the CAN bus. This interrupt causes the

MCP2510 to exit sleep mode. The interrupt is reset by

the MCU clearing the WAKIF bit.

ICOD<2:0>

Boolean Expression

000

ERRWAKTX0TX1TX2RX0RX1

001

ERR

010

ERRWAK

011

ERRWAKTX0

100

ERRWAKTX0TX1

101

ERRWAKTX0TX1TX2

110

ERRWAKTX0TX1TX2RX0

111

ERRWAKTX0TX1TX2RX0RX1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCZ33781EK | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO32 |

| MD1802FH | 10 A, 700 V, NPN, Si, POWER TRANSISTOR, TO-220AB |

| MD1802FX | 10 A, 700 V, NPN, Si, POWER TRANSISTOR |

| MD1803DFH | 10 A, 700 V, NPN, Si, POWER TRANSISTOR, TO-220AB |

| MD2001FX | 12 A, 700 V, NPN, Si, POWER TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCP2510T-I/SO | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Stand-alone CAN RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| MCP2510T-I/ST | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Stand-alone CAN RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| MCP2515 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:Stand-Alone CAN Controller With SPI Interface |

| MCP2515_12 | 制造商:MICROCHIP 制造商全稱:Microchip Technology 功能描述:Stand-Alone CAN Controller with SPI Interface |

| MCP2515DM-BM | 功能描述:網(wǎng)絡(luò)開發(fā)工具 CAN Bus Monitor Demo Board RoHS:否 制造商:Rabbit Semiconductor 產(chǎn)品:Development Kits 類型:Ethernet to Wi-Fi Bridges 工具用于評估:RCM6600W 數(shù)據(jù)速率:20 Mbps, 40 Mbps 接口類型:802.11 b/g, Ethernet 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。