- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25626 > MCIMX258CVM4 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 400 MHz, MICROPROCESSOR, PBGA400 PDF資料下載

參數(shù)資料

| 型號(hào): | MCIMX258CVM4 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA400 |

| 封裝: | 17 X 17 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, MAPBGA-400 |

| 文件頁(yè)數(shù): | 138/154頁(yè) |

| 文件大小: | 1498K |

| 代理商: | MCIMX258CVM4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)當(dāng)前第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)

i.MX25 Applications Processor for Consumer and Industrial Products, Rev. 8

84

Freescale Semiconductor

3.7.8

Enhanced Secured Digital Host Controller (eSDHCv2) Timing

figure. The following definitions apply to values and signals described in Table 61:

LS: low-speed mode. Low-speed card can tolerate clocks up to 400 kHz

FS: full-speed mode. Full-speed MMC card’s clock can reach 20 MHz; full speed SD/SDIO card

clock can reach 25 MHz

HS: high-speed mode. High-speed MMC card’s clock can reach 52 MHz; SD/SDIO card clock can

reach 50 MHz

86

SCKT rising edge to data out valid

—

18.0

13.0

x ck

i ck

ns

87

SCKT rising edge to data out high

impedance6

——

—

21.0

16.0

x ck

i ck

ns

88

SCKT rising edge to transmitter #0 drive

enable negation6

——

—

14.0

9.0

x ck

i ck

ns

89

FST input (bl, wr) setup time before SCKT

falling edge5

——

2.0

18.0

—

x ck

i ck

ns

90

FST input (wl) setup time before SCKT falling

edge

——

2.0

18.0

—

x ck

i ck

ns

91

FST input hold time after SCKT falling edge

—

4.0

5.0

—

x ck

i ck

ns

92

FST input (wl) to data out enable from high

impedance

——

—

21.0

—

ns

93

FST input (wl) to transmitter #0 drive enable

assertion

——

—

14.0

—

ns

94

Flag output valid after SCKT rising edge

—

14.0

9.0

x ck

i ck

ns

95

HCKR/HCKT clock cycle

—

2 x TC

15

—

ns

96

HCKT input rising edge to SCKT output

—

18.0

—

ns

97

HCKR input rising edge to SCKR output

—

18.0

—

ns

1 V

CORE_VDD = 1.00 ± 0.10 V; TJ = –40 °C to 125 °C, CL = 50 pF

2 In the “Characteristics” column, bl = bit length, wl = word length, wr = word length relative

3 In the “Expression” column, T

C = 7.5 ns.

4 For the internal clock, the external clock cycle is defined by Icyc and the ESAI control register.

5 The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync

signal waveform, but spreads starting from one serial clock before the first bit clock (same as the bit length frame sync signal),

until the second-to-last bit-clock of the first word in the frame.

6 Periodically sampled and not 100% tested.

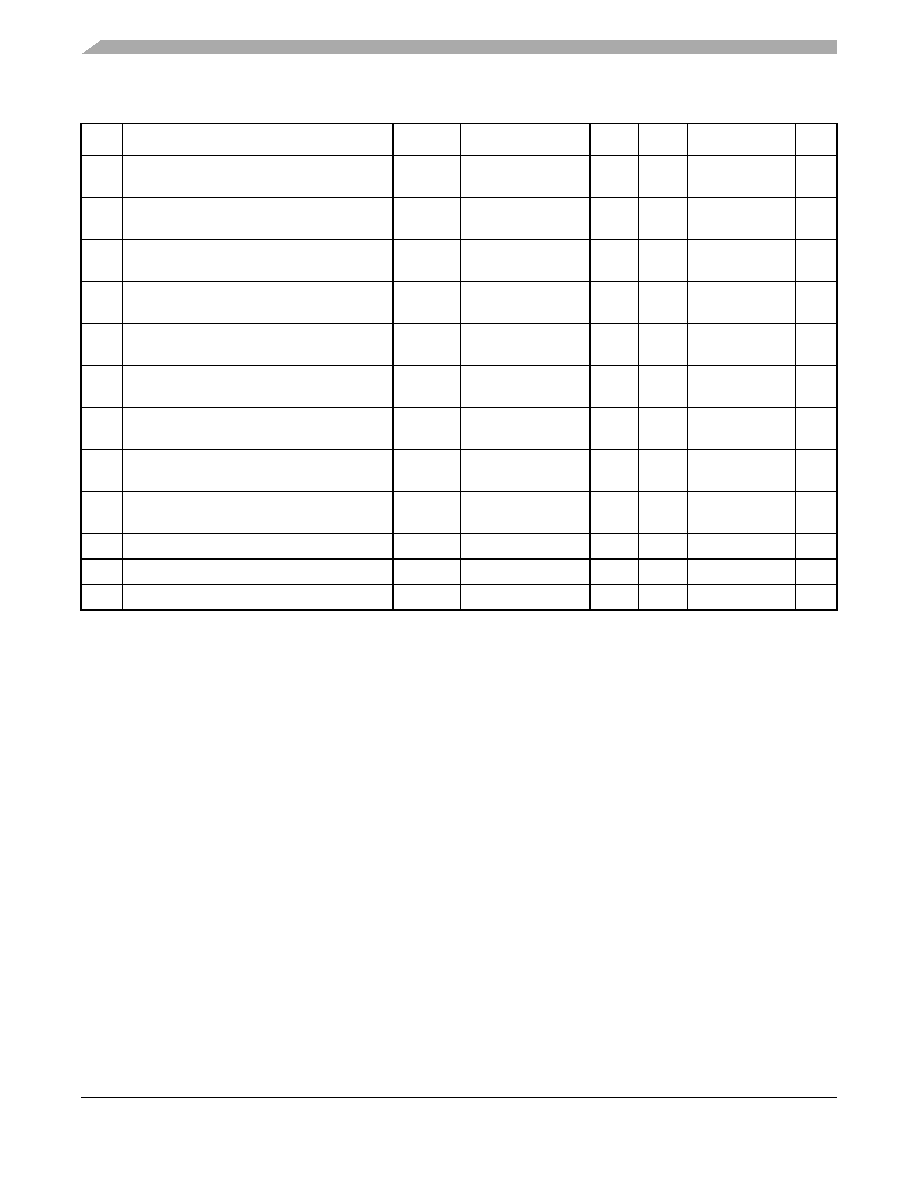

Table 60. ESAI General Timing Requirements (continued)

No.

Characteristics1 2

Symbol

Expression3

Min.

Max.

Condition

Unit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MD80C154-36/883D | 8-BIT, 36 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C52TXXX-16P883D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

| MC80C52XXX-30/883:D | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, CDIP40 |

| MD80C154-25/883 | 8-BIT, 25 MHz, MICROCONTROLLER, CDIP40 |

| MD80C154-20P883 | 8-BIT, 20 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCIMX25LPDK | 制造商:Freescale Semiconductor 功能描述:PRODUCT DEVELOPMENT KIT FOR THE I MX25 APPLICATIONS PROCESSO - Boxed Product (Development Kits) 制造商:Freescale Semiconductor 功能描述:KIT DEV I.MX25 FOR LINUX 制造商:Freescale 功能描述:Product Development Kit For The I.MX25 Applications Processor |

| MCIMX25LPDKJ | 功能描述:開(kāi)發(fā)板和工具包 - ARM HARDWARE RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評(píng)估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| MCIMX25LPDKJ | 制造商:Freescale Semiconductor 功能描述:; LEADED PROCESS COMPATIBLE:YES; PEAK RE |

| MCIMX25PDKCPUJ | 功能描述:開(kāi)發(fā)板和工具包 - ARM CPU BD, MX25, LINUXJ RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評(píng)估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

| MCIMX25WPDK | 功能描述:開(kāi)發(fā)板和工具包 - ARM MCIMX25 PDK ForLINUX RoHS:否 制造商:Arduino 產(chǎn)品:Development Boards 工具用于評(píng)估:ATSAM3X8EA-AU 核心:ARM Cortex M3 接口類型:DAC, ICSP, JTAG, UART, USB 工作電源電壓:3.3 V |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。