- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385568 > MC56F8345VFG60 (MOTOROLA INC) 56F8345 16-bit Hybrid Controller PDF資料下載

參數(shù)資料

| 型號: | MC56F8345VFG60 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 56F8345 16-bit Hybrid Controller |

| 中文描述: | 0-BIT, 240 MHz, OTHER DSP, PQFP128 |

| 封裝: | 14 X 20 MM, 0.50 MM PITCH, 1.40 MM HEIGHT, PLASTIC, LQFP-128 |

| 文件頁數(shù): | 77/148頁 |

| 文件大?。?/td> | 1420K |

| 代理商: | MC56F8345VFG60 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁

Register Descriptions

56F8345 Technical Data

Preliminary

77

5.6.5.5

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0

through 2. They are disabled by default.

GPIO A Interrupt Priority Level (GPIOA IPL)—Bits 5–4

00 = IRQ disabled (default)

01 = IRQ is priority level 0

10 = IRQ is priority level 1

11 = IRQ is priority level 2

5.6.5.6

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0

through 2. They are disabled by default.

GPIO B Interrupt Priority Level (GPIOB IPL)—Bits 3–2

00 = IRQ disabled (default)

01 = IRQ is priority level 0

10 = IRQ is priority level 1

11 = IRQ is priority level 2

5.6.5.7

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0

through 2. They are disabled by default.

GPIO C Interrupt Priority Level (GPIOC IPL)—Bits 1–0

00 = IRQ disabled (default)

01 = IRQ is priority level 0

10 = IRQ is priority level 1

11 = IRQ is priority level 2

5.6.6

Interrupt Priority Register 5 (IPR5)

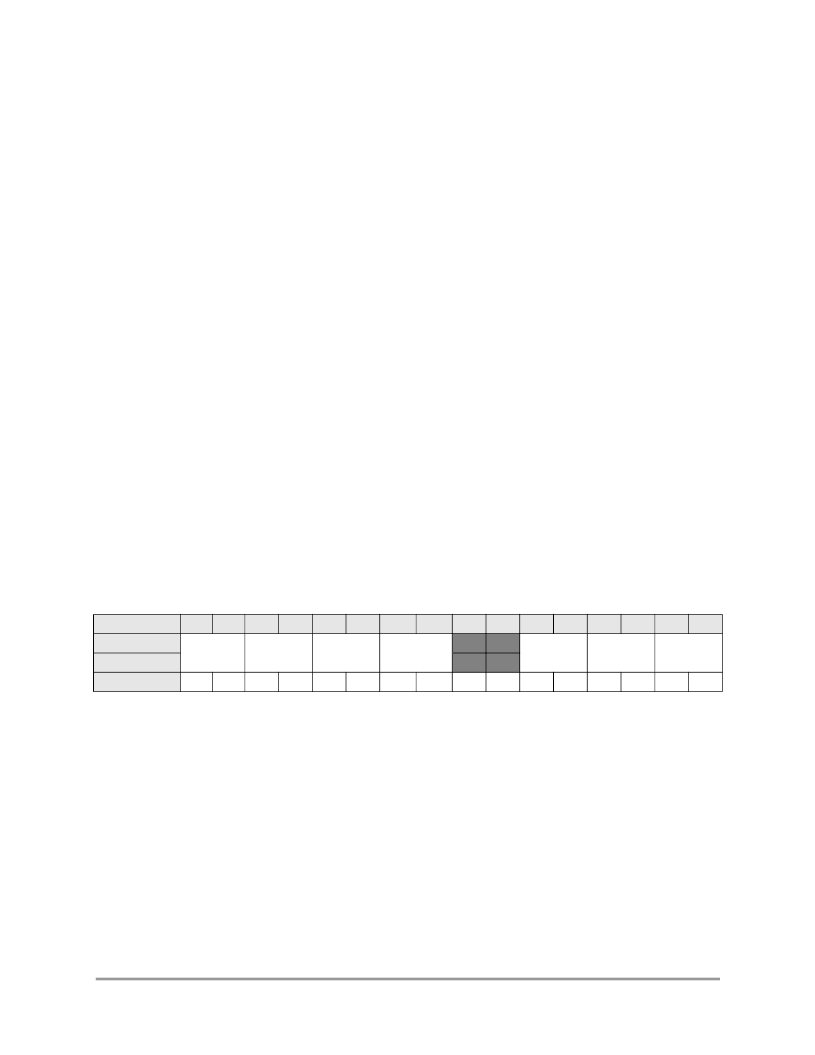

Figure 5-8 Interrupt Priority Register 5 (IPR5)

5.6.6.1

Quadrature Decoder 1 INDEX Pulse Interrupt Priority Level

(DEC1_XIRQ IPL)—Bits 15–14

This field is used to set the interrupt priority level for IRQs. This IRQ is limited to priorities 0

through 2. They are disabled by default.

00 = IRQ disabled (default)

01 = IRQ is priority level 0

10 = IRQ is priority level 1

11 = IRQ is priority level 2

Base + $5

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Read

DEC1_XIRQ

IPL

DEC1_HIRQ

IPL

SCI1_RCV

IPL

SCI1_RERR

IPL

0

0

SCI1_TIDL

IPL

SCI1_XMIT

IPL

SPI0_XMIT

IPL

Write

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC912B32FU8 | Evaluation Board |

| MC74AC14 | Hex Inverter Schmitt Trigger(六反相施密特觸發(fā)器) |

| MC74AC273 | Octal D Flip Flop(八D觸發(fā)器) |

| MC74AC32 | Quad 2(四2輸入或門) |

| MC74AC373 | Octal Transparent Latch with 3 State Outputs(八D鎖存器(三態(tài)輸出)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC56F8345VFGE | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16 BIT HYBRID CONTROLLER RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| MC56F8346 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| MC56F8346EVM | 制造商:Freescale Semiconductor 功能描述:Tools Development kit Kit Contents:Inst |

| MC56F8346MFV60 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 60MHz 60MIPS RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| MC56F8346MFVE | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16 BIT HYBRID CONTROLLER RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。