- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377894 > MB86602C (Fujitsu Limited) SCSI-II Protocol Controller (Differential)(SCSI-II 協(xié)議控制器) PDF資料下載

參數(shù)資料

| 型號: | MB86602C |

| 廠商: | Fujitsu Limited |

| 英文描述: | SCSI-II Protocol Controller (Differential)(SCSI-II 協(xié)議控制器) |

| 中文描述: | 支持SCSI - II協(xié)議控制器(差異)(支持SCSI - II協(xié)議控制器) |

| 文件頁數(shù): | 7/57頁 |

| 文件大?。?/td> | 487K |

| 代理商: | MB86602C |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

MB86602C

7

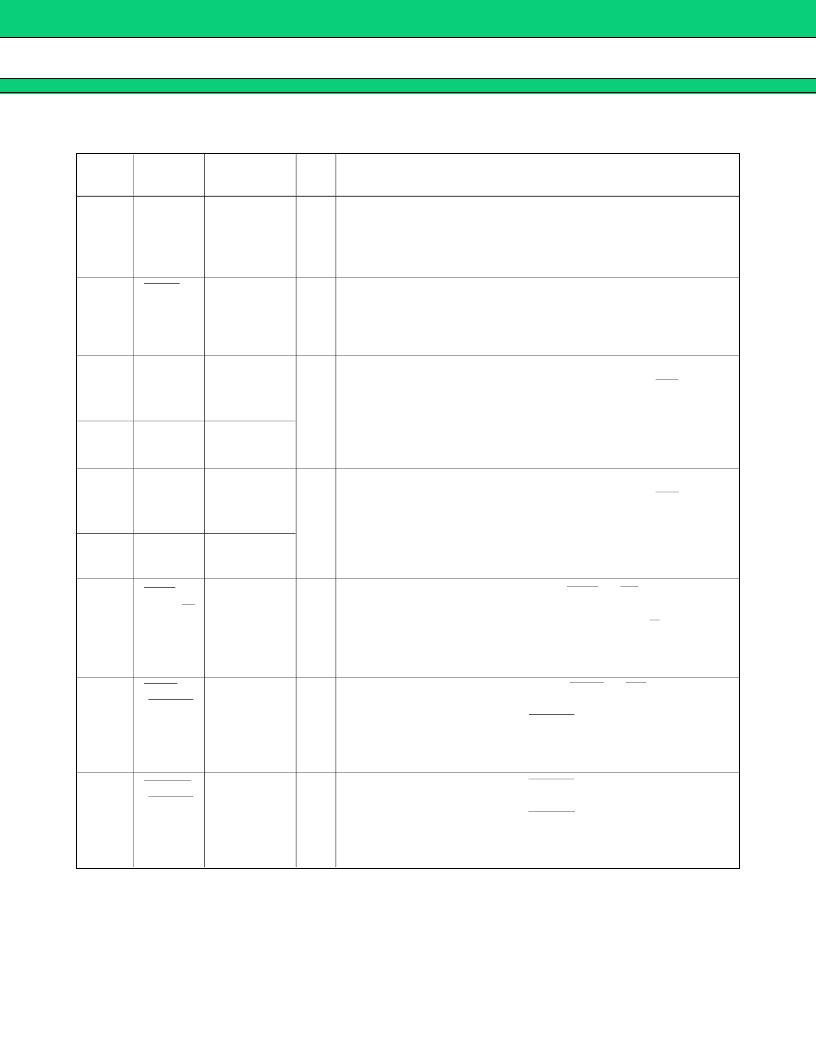

Outputs the DMA transfer request signal to a DMA controller.

Requests data transfer between SPC and memory via the DMA

bus.

Active “H” signal.

Inputs the DMA enable signal from a DMA controller.

When this input signal is active, the DMA cycle (read/write) is

executed.

Active “L” signal.

Inputs and outputs the DMA data upper byte and parity signal.

Directly connected to the MPU data bus when the CS1 input is

valid.

Inputs and outputs the DMA data lower byte and parity signal.

Directly connected to the MPU data bus when the CS1 input is

valid.

For 80-series Mode, inputs the signal (IORD or RD) for the SPC to

output data to the DMA bus. Active “L” signal.

For 68-series Mode, inputs the control signal (DMR/W) for a DMA

controller to output/input data to the SPC.

Active “H” for output and active “L” for input.

For 80-series Mode, inputs the signal (IOWR or WR) for DMA bus

data to be input to the SPC.

For 68-series Mode, inputs the DMLDS signal output by the DMA

controller when the DMA data bus lower byte is valid.

Active “L” signal.

For 80-series mode, inputs the DMBHE signal output by the DMA

controller when the data bus upper byte is valid.

For 68-series mode, inputs the DMUDS signal output by the DMA

controller when data bus upper byte is valid.

Active “L” signal.

Description

Pin

number

I/O

Pin name

Pin

symbol

3. DMA Interface

52

DMA request

DREQ

O

51

DMA

acknowledge

DACK

I

48, 47, 46,

45, 44, 43,

42, 41

DMA data 15

to

DMA data 8

DMD15

to

DMD8

I/O

49

Upper DMA

data parity

UDMDP

39, 38, 37,

36, 35, 34,

33, 32

DMA data 7

to

DMA data 0

DMD7

to

DMD0

I/O

31

Lower DMA

data parity

LDMDP

27

I/O read

(DMA read/

write)

IORD

(DMR/W)

I

26

I/O write

(DMA lower

data strobe)

IOWR

(DMLDS)

I

50

DMA bus

high enable

(DMA upper

data strobe)

DMBHE

(DMUDS)

I

*: The pin symbols in parenthesis ( ) are applicable when the MODE input is “L”.

(Continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB86603 | Communication Control SCSI-II Protocol Controller(通信控制SCSI-II協(xié)議控制器) |

| MB86604L | Low Power 5V RS232 Dual Driver/Receiver with 0.1?μF Capacitors; Package: SO; No of Pins: 16; Temperature Range: -40?°C to 85?°C |

| MB86604 | Low Power 5V RS232 Dual Driver/Receiver with 0.1?μF Capacitors; Package: SO; No of Pins: 16; Temperature Range: -40?°C to 85?°C |

| MB86604LPFV | Low Power 5V RS232 Dual Driver/Receiver with 0.1?μF Capacitors; Package: SO; No of Pins: 16; Temperature Range: -40?°C to 85?°C |

| MB86605 | SCSI-II Protocol Controller(with PCI interface)(SCSI-II 協(xié)議控制器(帶PCI接口)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB86604 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:SCSI-II Protocol Controller (with single-ended driver/receiver) |

| MB86604L | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:SCSI-II Protocol Controller (with single-ended driver/receiver) |

| MB86604LPFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:SCSI-II Protocol Controller (with single-ended driver/receiver) |

| MB86606A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FAST-20 SCSI Protocol Controller |

| MB86606APMT2 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:FAST-20 SCSI Protocol Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。