- 您現在的位置:買賣IC網 > PDF目錄69257 > PTPS659104A1RSLR (TEXAS INSTRUMENTS INC) POWER SUPPLY SUPPORT CKT, PQCC48 PDF資料下載

參數資料

| 型號: | PTPS659104A1RSLR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | POWER SUPPLY SUPPORT CKT, PQCC48 |

| 封裝: | 6 X 6 MM, 1 MM HEIGHT, GREEN, PLASTIC,VQFN-48 |

| 文件頁數: | 22/89頁 |

| 文件大小: | 941K |

| 代理商: | PTPS659104A1RSLR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

PRODUCTPREVIEW

SWCS046-018

PWRHOLD

VIO/VFBIO

VAUX1

VDD2/VFB2

VDD1/VFB1

VPLL

VDAC

VAUX2

VMMC

CLK32KOUT

NRESPWRON

t

dSOFF2

t

dSON1

1.8 V

3.3 V

t

dSON2

t

dSON3

1.2 V

1.8 V

t

dSON4

t

dSON5

1.8 V

t

dSON6

t

dSON7

3.3 V

t

dSON8

t

dSOFF1

Switch-off sequence

t

: Switch-on sequence

dSONT

www.ti.com

SWCS046C – MARCH 2010 – REVISED JUNE 2010

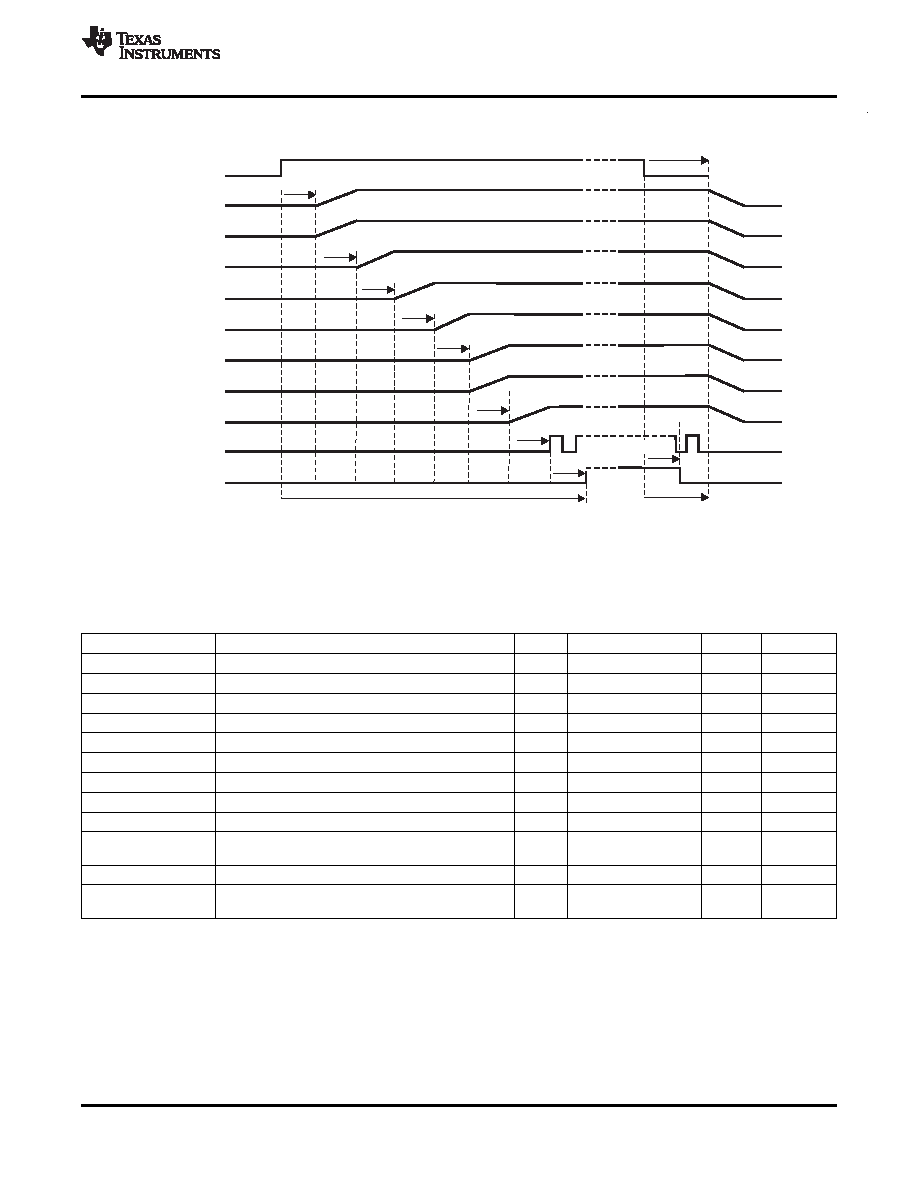

Figure 2 shows the 00 Boot mode timing characteristics.

Figure 2. Boot Mode: BOOT1 = 0, BOOT0 = 0

Table 3 lists the 00 Boot mode timing characteristics.

Table 3. Boot Mode: BOOT1 = 0, BOOT0 = 0 Timing Characteristics

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

tdSON1

PWRHOLD rising edge to VIO, VAUX1 enable delay

66 × tCK32k = 2060

s

tdSON2

VIO to VDD2 enable delay

64 × tCK32k = 2000

s

tdSON3

VDD2 to VDD1 enable delay

64 × tCK32k = 2000

s

tdSON4

VDD1 to VPLL enable delay

64 × tCK32k = 2000

s

tdSON5

VPLL to VDAC,VAUX2 enable delay

64 × tCK32k = 2000

s

tdSON6

VDAC to VMMC enable delay

64 × tCK32k = 2000

s

VMMC to CLK32KOUT rising edge delay

64 × tCK32k = 2000

s

tdSON8

CLK32KOUT to NRESPWON rising edge delay

64 × tCK32k = 2000

s

tdSONT

Total switch-on delay

16

ms

PWRHOLD falling edge to NRESPWON falling edge

tdSOFF1

2 × tCK32k = 62.5

s

delay

tdSOFF1B

NRESPWON falling edge to CLK32KOUT low delay

3 × tCK32k = 92

s

PWRHOLD falling edge to supplies and reference

tdSOFF2

5 × tCK32k = 154

s

disable delay

Registers default setting: CK32K_CTRL = 1 (32-kHz RC oscillator is used), RTC_PWDN = 1 (RTC domain off),

IT_POL = 0 (INt2 interrupt flag active low), VMBHI_IT_MSK = 0 (automatic switch-on on Battery plug),

VMBCH_SEL = 11.

BOOT1 = 0, BOOT0 = 1

Table 4 provides details about the EEPROM setting for the BOOT modes. The power-up sequence for this boot

mode is provided in Figure 3.

Copyright 2010, Texas Instruments Incorporated

29

相關PDF資料 |

PDF描述 |

|---|---|

| PTPS659107A1RSL | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659105A1RSLR | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659103A1RSL | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659108A1RSLR | POWER SUPPLY SUPPORT CKT, PQCC48 |

| PTPS659106A1RSL | POWER SUPPLY SUPPORT CKT, PQCC48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| PTPS659109A1RSL | 制造商:Texas Instruments 功能描述: |

| PTPS6591102A2ZRCR | 制造商:TI 功能描述:TPS65911 |

| PTPS6591102ZRC | 制造商:TI 功能描述:TPS65911 |

| PTPS6591104A2ZRCR | 制造商:TI 功能描述:TPS65911 |

| PTPS659110A2ZRC | 制造商:TI 功能描述:TPS65911 |

發(fā)布緊急采購,3分鐘左右您將得到回復。