- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384643 > M66290AGP (Mitsubishi Electric Corporation) USB DEVICE CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | M66290AGP |

| 廠(chǎng)商: | Mitsubishi Electric Corporation |

| 英文描述: | USB DEVICE CONTROLLER |

| 中文描述: | USB設(shè)備控制器 |

| 文件頁(yè)數(shù): | 39/53頁(yè) |

| 文件大小: | 435K |

| 代理商: | M66290AGP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)當(dāng)前第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

USB DEVICE CONTROLLER

M66290AGP/FP

MITSUBISHI <DIGITAL ASSP>

39

Set the maximum data size (Byte) to transmit/receive in one packet

transfer.

Set the value of wMaxPacketSize in request.

When this bit is set to "1", FIFO data register becomes 8-bit mode and

when accessed "FIFO Data Register" of endpoint, lower 8bit[7:0]

becomes effective.

When transmit odd number of byte, it is needed to write in 8-bit mode.

When read in 8-bit mode, set to 8-bit mode before data receive.

When the selected endpoint is set to OUT and if this bit is set to "1",

OUT buffer effective flag and read data (number of byte) is cleared.

In this state(OUT buffer does not become effective state), SIE side

writes data from host into OUT buffer but CPU side does not read.

When set this bit to "1", whatever the transfer direction is, endpoint

buffer (all buffer of single/double buffer) are cleared.

When clear the endpoint buffer, set this bit to "1" and then set again to "0".

To set this bit as "1", Null data addition transmit mode is set .

In the endpoint which is set to continuous transmit mode, when

write a multiple data of maximum packet size into buffer and transmit,

Null data is transmitted automatically after transmitted the last packet.

This setting is effective when continuous transmit mode is set.

Set response PID.

00 : NAK Whatever the buffer state is, do NAK handshake.

01 : BUF Response PID is selected according to the state of buffer

and sequence toggle bit. (In bulk/interrupt transfer, one of

ACK, NAK, DATA0, and DATA1)

1x : STALL Do STALL handshake.

If the transfer direction of selected endpoint is OUT, when received

data which exceeded maximum packet size (MXPS), it becomes

"1x" (=STALL) automatically.

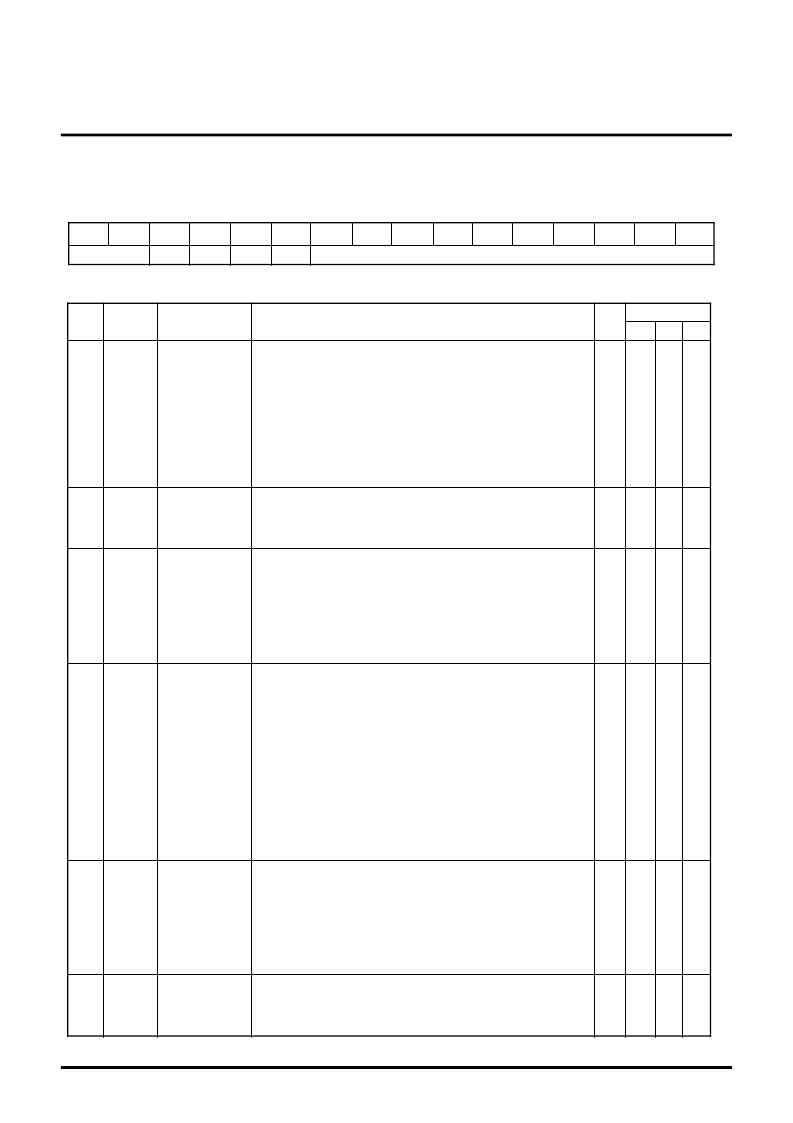

Bit

Bit

Name

Name

Function

Reset

-

-

0

W/R

Null data

addition

transmit mode

-

-

040h

W/R

-

-

0

W/R

-

-

0

W/R

-

-

0

W/R

-

-

00

W/R

10

EPi_

NULMD

EPi_

ACLR

Set the access mode to endpoint buffer.

0 : CPU access mode

1 : DMA transfer mode

Max Packet size

EPi_

MXPS

[9:0]

FIFO access

8 bit mode

EPi_Octl

OUT buffer

automatic

clear mode

DMA transfer mode

EPi_

DMAMD

Response PID

EPi_

PID

[1:0]

11

12

9 to 0

13

15, 14

W/R

USB

S/W

H/W

NULMD

DMAMD

EPi_MXPS[9:0]

Octl

ACLR

EPi_PID[1:0]

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D15

D13

D14

(4-8) EPi Configuration Register 1 ( i=1 to 5 )

(Address : EP1=62h, EP2=66h, EP3=6Ah, EP4=6Eh, EP5=72h)

The EPi configuration register 1 must be set in a state of response PID is NAK("00").

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M66300FP | PARALLEL-IN SERIAL-OUT DATA BUFFER WITH FIFO |

| M66300P | PARALLEL-IN SERIAL-OUT DATA BUFFER WITH FIFO |

| M66305AFP | TOGGLE LINE BUFFER |

| M66305AP | TOGGLE LINE BUFFER |

| M66310FP | 16-BIT LED DRIVER WITH SHIFT REGISTER AND LATCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66291GP | 制造商:Renesas Electronics Corporation 功能描述: |

| M66291GP#201 | 制造商:Renesas Electronics Corporation 功能描述:IC ASSP USB2.0 DEVICE CONTROLLER 48LQFP |

| M66291GP#RB0S | 功能描述:IC USB CONTROLLER GEN-PUR 48LQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類(lèi)型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱(chēng):Q6396337A |

| M66291GPRB0S | 制造商:Renesas Electronics Corporation 功能描述:USB2.0 Device Controller,LQFP48 |

| M66291HP | 制造商:RENESAS 制造商全稱(chēng):Renesas Technology Corp 功能描述:ASSP (USB2.0 Device Controller) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。