- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370973 > M5M4V64S20ATP-8L (Mitsubishi Electric Corporation) 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | M5M4V64S20ATP-8L |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| 中文描述: | 64M號(4銀行甲4194304字× 4位)同步DRAM |

| 文件頁數(shù): | 19/48頁 |

| 文件大?。?/td> | 1097K |

| 代理商: | M5M4V64S20ATP-8L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

M5M4V64S20ATP-8, -10, -12

Jan'97

Preliminary

MITSUBISHI LSIs

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM

MITSUBISHI ELECTRIC

SDRAM (Rev.0.2)

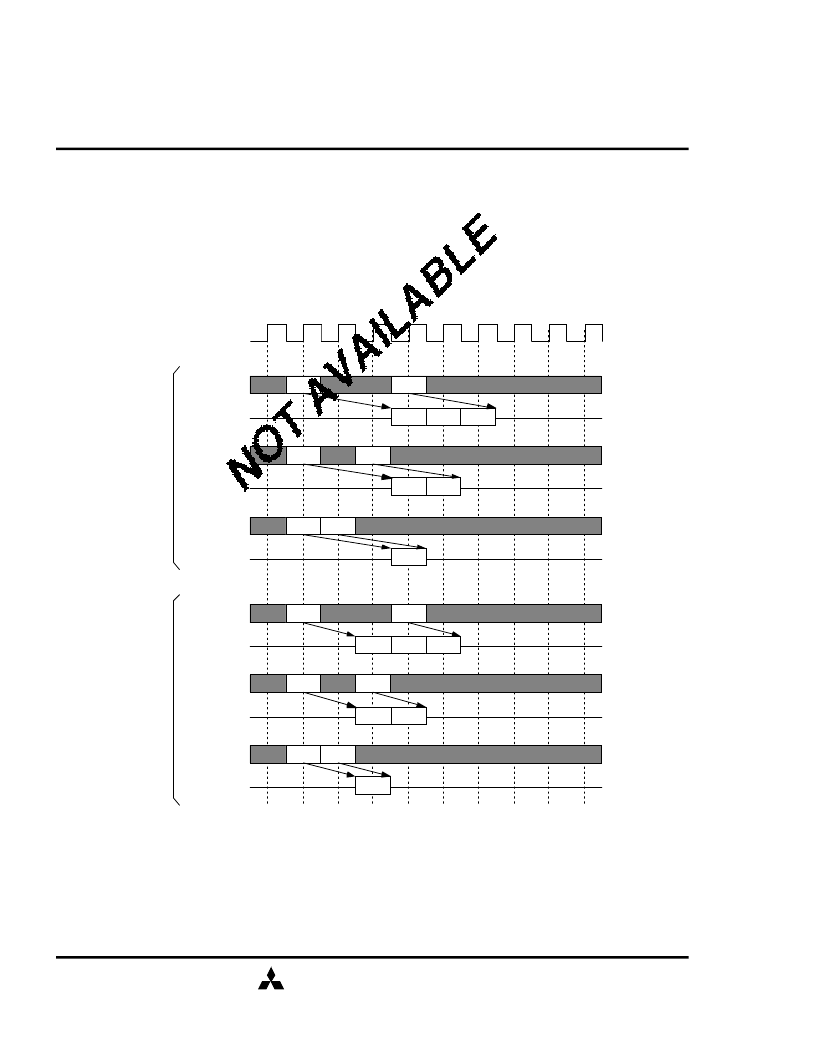

[ Read Interrupted by Burst Terminate ]

Similarly to the precharge, burst terminate command can interrupt burst read operation and disable the

data output. The terminated banl remains active. READ to TERM interval is minimum 1 CLK. A TERM

command to output disable latency is equivalent to the /CAS Latency. As a result, READ to TERM interval

determines valid data length to be output. The figure below shows examples of BL=4.

Read Interrupted by Burst Terminate (BL=4)

CLK

CL=3

Command

DQ

READ

TERM

Q0

Q1

Q2

Command

DQ

READ

TERM

Q0

CL=2

Command

DQ

READ

TERM

Q0

Q1

Q2

Command

DQ

READ

TERM

Q0

Command

DQ

READ TERM

Q0

Q1

Command

DQ

READ TERM

Q0

Q1

19

相關PDF資料 |

PDF描述 |

|---|---|

| M5M51008KR-10L | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

| M5M51008KR-10LL | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

| M5M51008KR-55L | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

| M5M51008KR-55LL | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

| M5M51008BP-10L | 1048576-BIT(131072-WORD BY 8-BIT)CMOS STATIC RAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V64S30ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM |

| M5M4V64S30ATP-10L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM |

| M5M4V64S30ATP-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM |

| M5M4V64S30ATP-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM |

| M5M4V64S30ATP-8A | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。