- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69016 > M41ST87YMX6 (STMICROELECTRONICS) 1 TIMER(S), REAL TIME CLOCK, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | M41ST87YMX6 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 時(shí)鐘/數(shù)據(jù)恢復(fù)及定時(shí)提取 |

| 英文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| 封裝: | 0.300 INCH, ROHS COMPLIANT, PLASTIC, SOX-28 |

| 文件頁數(shù): | 9/52頁 |

| 文件大小: | 689K |

| 代理商: | M41ST87YMX6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

M41ST87Y, M41ST87W

Operating modes

Doc ID 9497 Rev 8

2.3

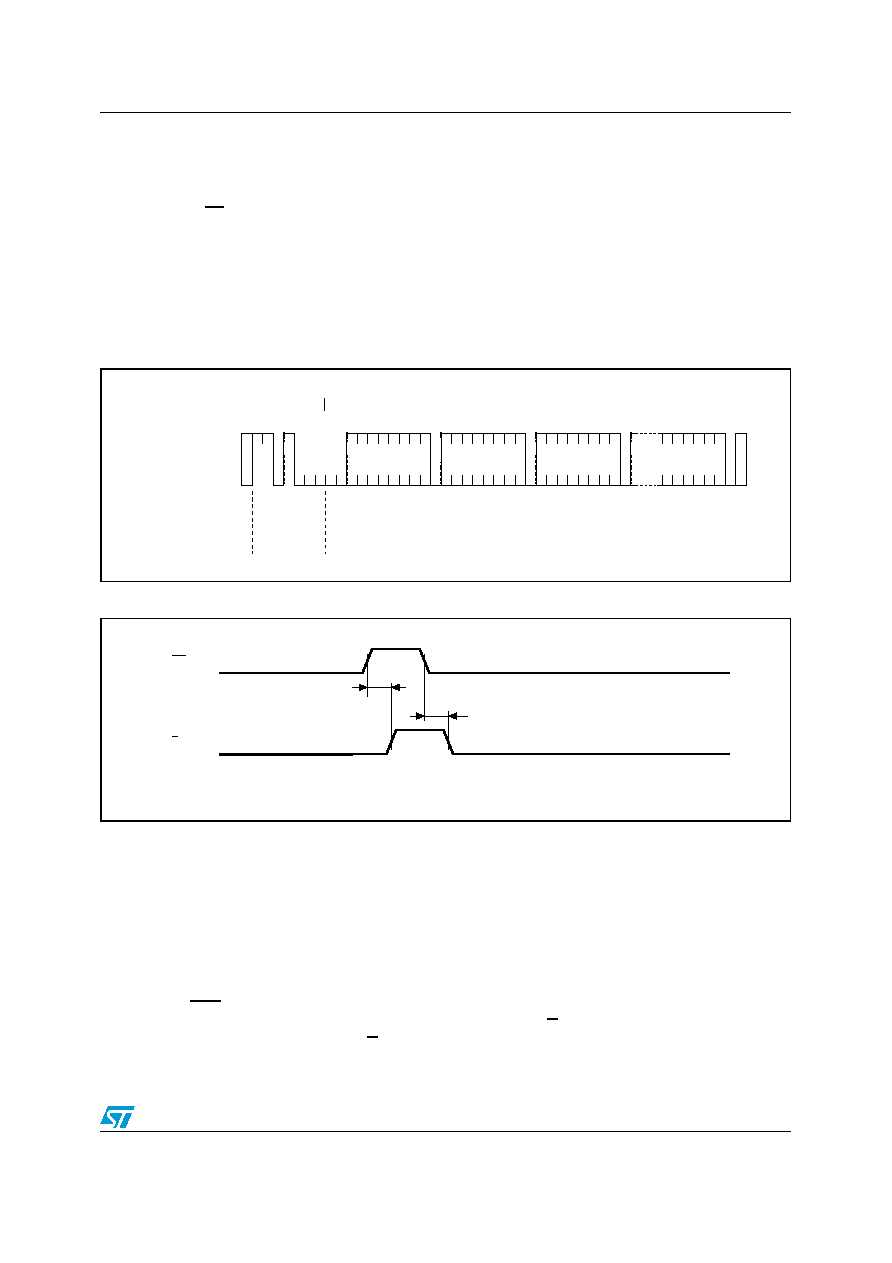

WRITE mode

In this mode the master transmitter transmits to the M41ST87Y/W slave receiver. Bus

protocol is shown in Figure 12. Following the START condition and slave address, a logic '0'

(R/W = 0) is placed on the bus and indicates to the addressed device that word address An

will follow and is to be written to the on-chip address pointer. The data word to be written to

the memory is strobed in next and the internal address pointer is incremented to the next

memory location within the RAM on the reception of an acknowledge clock. The

M41ST87Y/W slave receiver will send an acknowledge clock to the master transmitter after

it has received the slave address (see Figure 9 on page 16) and again after it has received

the word address and each data byte.

Figure 12.

WRITE mode sequence

Figure 13.

WRITE cycle timing: RTC & external SRAM control signals

1.

Available in SOX28 (MX) package only.

2.4

Data retention mode

With valid VCC applied, the M41ST87Y/W can be accessed as described above with READ

or WRITE cycles. Should the supply voltage decay, the M41ST87Y/W will automatically

deselect, write protecting itself (and any external SRAM) when VCC falls between VPFD

accomplished by internally inhibiting access to the clock registers. At this time, the reset pin

(RST) is driven active and will remain active until VCC returns to nominal levels. External

RAM access is inhibited in a similar manner by forcing ECON to a high level. This level is

within 0.2 volts of the VBAT. ECON will remain at this level as long as VCC remains at an out-

of-tolerance condition. When VCC falls below the battery backup switchover voltage (VSO),

AI00591

BUS ACTIVITY:

AC

K

S

AC

K

AC

K

AC

K

AC

K

ST

OP

ST

AR

T

P

SDA LINE

BUS ACTIVITY:

MASTER

R/W

DATA n

DATA n+1

DATA n+X

WORD

ADDRESS (An)

SLAVE

ADDRESS

AI03663

EX

(1)

ECON

(1)

tEXPD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M41ST87YMX6TR | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M41ST87WMX6TR | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M41ST95WMX6 | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M41ST95YMH6E | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| M41ST95YMH6 | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M41ST87YMX6F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 V and 3.3/3.0 V secure serial RTC and NVRAM supervisor with tamper detection and 128 bytes of clearable NVRAM |

| M41ST87YMX6TR | 功能描述:實(shí)時(shí)時(shí)鐘 Serial 1280 (160x8) RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時(shí)間格式:HH:MM:SS RTC 存儲(chǔ)容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| M41ST87YSS6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 V and 3.3/3.0 V secure serial RTC and NVRAM supervisor with tamper detection and 128 bytes of clearable NVRAM |

| M41ST87YSS6F | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 V and 3.3/3.0 V secure serial RTC and NVRAM supervisor with tamper detection and 128 bytes of clearable NVRAM |

| M41ST95W | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5.0 or 3.0V, 512 bit (64 bit X 8) Serial RTC (SPI) SRAM and NVRAM Supervisor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。