- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98007 > M38827G5-XXXHP 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | M38827G5-XXXHP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件頁數(shù): | 37/64頁 |

| 文件大小: | 619K |

| 代理商: | M38827G5-XXXHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Rev.1.01

Nov 14, 2005

page 40 of 60

REJ03B0089-0101

3882 Group

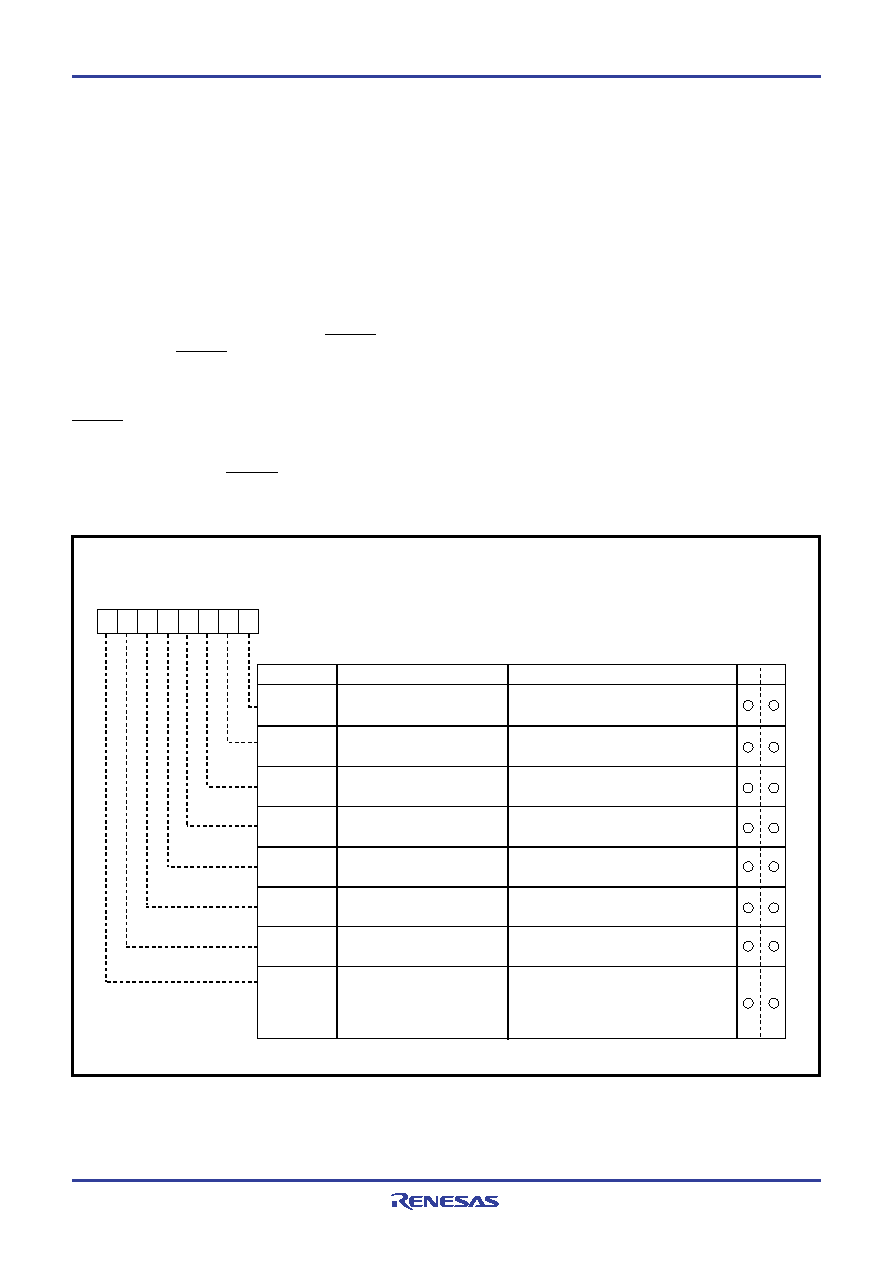

Fig. 32 Configuration of serialized IRQ control register

Register Explanation

The serialized IRQ function is configured and controlled by the se-

rialized IRQ request register (SERIRQ) and the serialized IRQ

control register (SERCON).

[Serialized IRQ control register (SERCON)] 001D16

Bit 0 : Serialized IRQ enable bit (SIRQEN )

This bit enables/disables the serialized IRQ interface. When this

bit is “1”, use of serialized IRQ is enabled. Then P87 functions as

IRQ/Data line (SERIRQ) and P47 functions as CLKRUN.

Output structure of CLKRUN pin becomes N-channel open drain.

Bit 1 : LPC clock restart enable bit (RUNEN )

Setting this bit to “1” enables clock restart with “L” output of

CLKRUN.

Bit 2 : LPC clock stop inhibition bit (SUPEN )

Setting this bit to “1” makes CLKRUN output change to “L” for in-

hibiting the clock stop.

Bit 3 : Hardware IRQ1 request bit (SEIR1)

When this bit is “1”, OBF0 status is directly connected to the IRQ1

frame.

Bit 4 : Hardware IRQ12 request bit (SEIR12 )

When this bit is “1”, OBF0 status is directly connected to IRQ12

frame.

Bit 5 : Hardware IRQx request bit (SEIRx )

When this bit is “1”, OBF1 status is directly connected to the IRQx

frame.

Bit 6 : IRQ1/IRQ12 disable bit (SCH0EN )

This bit controls whether the serialized IRQ channel 0 transfers

the IRQ1 and IRQ12 frame to the host or not.

Bit 7 : IRQx output polarity bit (SCH1POL)

This bit selects IRx frame output level.

Serialized IRQ control register

Bit name

Function

Bit symbol

W

R

Symbol

Address

When reset

SERCON

001D16

000000002

SIRQEN

Serialized IRQ enable bit

0 : Serialized IRQ disable

1 : Serialized IRQ enable

0 : Clock restart disable

1 : Clock restart enable

0 : Stop inhibition control disable

1 : Stop inhibition control enable

0 : No IRQ1 request

1 : OBF0 synchronized IRQ1 request

LPC clock restart enable bit

LPC clock stop inhibition bit

Hardware IRQ1 request bit

RUNEN

SUPEN

SEIR1

b7

b6

b5

b4

b3

b2

b1

b0

Hardware IRQ12 request bit

0 : No IRQ12 request

1 : OBF0 synchronized IRQ12 request

SEIRx

Hardware IRQx request bit

0 : No IRQx request

1 : OBF1 synchronized IRQx request

SEIR12

SCH0EN

IRQ1/IRQ12 disable bit

0 : IRQ1/IRQ12 output enable

1 : IRQ1/IRQ12 output disable

IRQx output polarity bit

0 : -Request Hiz-Hiz-Hiz

-No request L-H-Hiz

1 : -Request L-H-Hiz

-No request Hiz-Hiz-Hiz

SCH1POL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38869MFAHP | 8-BIT, FLASH, 10 MHz, MICROCONTROLLER, PQFP80 |

| M38B57MC-XXXFP | 8-BIT, MROM, 4.19 MHz, MICROCONTROLLER, PQFP80 |

| M38B79FFFP | 8-BIT, FLASH, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| M38B79MFH-XXXXFP | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| M38C13M6-XXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M38827G6-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38827G7-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38827G8-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38827G9-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38827GA-XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。