- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45037 > M37754M8C-XXXHP 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | M37754M8C-XXXHP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | 0.50 MM PITCH, FINE PITCH, PLASTIC, QFP-100 |

| 文件頁數(shù): | 25/114頁 |

| 文件大小: | 1116K |

| 代理商: | M37754M8C-XXXHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

MITSUBISHI MICROCOMPUTERS

M37754M8C-XXXGP, M37754M8C-XXXHP

M37754S4CGP, M37754S4CHP

18

PRELIMINAR

Y

Notice:

This

is not

a final

specification.

Some

parametric

limits

are

subject

to change.

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

INTERRUPTS

Table 2 shows the interrupt types and the corresponding interrupt

vector addresses. Reset is also treated as a type of interrupt and is

discussed in this section, too.

___

DBC is an interrupt used during debugging.

___

Interrupts other than reset, DBC, watchdog timer, zero divide, and

BRK instruction all have interrupt control registers. Table 3 shows the

addresses of the interrupt control registers and Figure 10 shows the

bit configuration of the interrupt control register.

The interrupt request bit is automatically cleared by the hardware

during reset or when processing an interrupt. Also, interrupt request

___

bits other than DBC and watchdog timer can be cleared by software.

____

___

INT4 to INT0 are external interrupts; whether to cause an interrupt at

the input level (level sense) or at the edge (edge sense) can be se-

lected with the level/edge select bit. Furthermore, the polarity of the

interrupt input can be selected with the polarity select bit.

___

__

In the INT3 external interrupt, the INT3 input, KI3 to KI0 inputs, or KI4

__

____

to KI0 inputs can be selected with bits 7 and 6 of INT3 interrupt con-

trol register.

Timer and UART interrupts are described in the respective section.

The priority of interrupts when multiple interrupts are caused simul-

taneously is partially fixed by hardware, but, it can also be adjusted

by software as shown in Figure 11.

The hardware priority is fixed as the following:

___

reset > DBC > watchdog timer > other interrupts

Table 2. Interrupt types and the interrupt vector addresses

Interrupts

____

INT4 external interrupt

____

INT3 external interrupt

A-D

UART1 transmit

UART1 receive

UART0 transmit

UART0 receive

Timer B2

Timer B1

Timer B0

Timer A4

Timer A3

Timer A2

Timer A1

Timer A0

____

INT2 external interrupt

____

INT1 external interrupt

____

INT0 external interrupt

Watchdog timer

____

DBC (Do not select.)

Break instruction

Zero divide

Reset

Vector addresses

00FFD216

00FFD316

00FFD416

00FFD516

00FFD616

00FFD716

00FFD816

00FFD916

00FFDA16

00FFDB16

00FFDC16

00FFDD16

00FFDE16

00FFDF16

00FFE016

00FFE116

00FFE216

00FFE316

00FFE416

00FFE516

00FFE616

00FFE716

00FFE816

00FFE916

00FFEA16

00FFEB16

00FFEC16

00FFED16

00FFEE16

00FFEF16

00FFF016

00FFF116

00FFF216

00FFF316

00FFF416

00FFF516

00FFF616

00FFF716

00FFF816

00FFF916

00FFFA16

00FFFB16

00FFFC16

00FFFD16

00FFFE16

00FFFF16

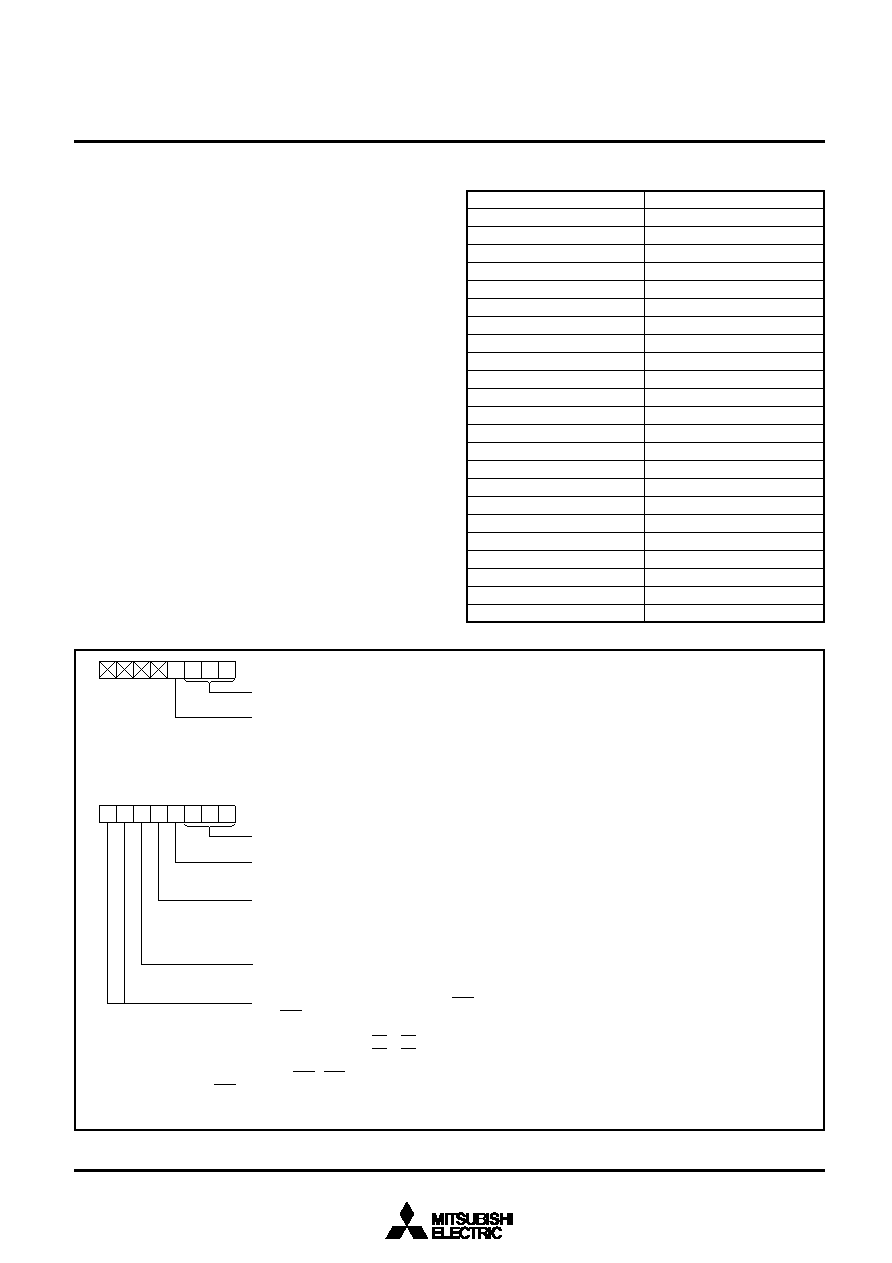

Fig. 10 Interrupt control register bit configuration

76543210

Interrupt priority level

Interrupt request bit (Note 1)

0 : No interrupt

1 : Interrupt

76543210

Interrupt priority level

Interrupt request bit

0 : No interrupt

1 : Interrupt

Polarity select bit

0 : Set interrupt request bit at “H” level for level sense and when changing from “H” to “L”

level for edge sense.

1 : Set interrupt request bit at “L” level for level sense and when changing from “L” to “H”

level for edge sense.

Level/Edge select bit

0 : Edge sense

1 : Level sense

Key input interrupt select bits 1, 0 (only for INT3 interrupt control register)

0 0 : INT3 interrupt selected

0 1 : Do not select.

1 0 : Key input interrupt (KI3 to KI0) selected

1 1 : Key input interrupt (KI4 to KI0) selected

Interrupt control register configuration for A-D converter, UART0, UART1, timer A0 to timer A4, and timer B0 to timer B2.

Note 1: The A-D conversion interrupt request bit becomes undefined after reset. Clear this bit to “0” before use of the A-D conversion interrupt.

Interrupt control register configuration for INT4– INT0 (Note 2).

Note 2: The contents of INT4 interrupt control register after reset cannot be changed unless bit 5 of the particular function select register 1 (see

Figure 15) is set to “1.”

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37754S4CHP | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754S4CHP | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37754M8C-XXXGP | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| M37777E9AGS | 16-BIT, UVPROM, 16 MHz, MICROCONTROLLER, CQCC100 |

| M34550M6A-XXXFP | 4-BIT, MROM, 1.6 MHz, MICROCONTROLLER, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37754S4CGP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16BIT CMOS MICROCOMPUTER |

| M37754S4CHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M3775PR-H400CL | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-0.75A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

| M3775RK-C0.50A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING RESISTOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。