- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67763 > M37643F8HP 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | M37643F8HP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 12 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件頁數(shù): | 52/120頁 |

| 文件大小: | 1253K |

| 代理商: | M37643F8HP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當(dāng)前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

37

7643 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

PRELIMINAR

Y

Notice:

This

is not

a final

specification.

Some

parametric

limits

are

subject

to

change.

DMAC index and status register (address 003F16)

DMAIS

DMAC channel 0 count register underflow flag (D0UF)

0: No underflow

1: Underflow generated

DMAC channel 0 suspend flag (D0SFI)

0: Not suspended

1: Suspended

DMAC channel 1 count register underflow flag (D1UF)

0: No underflow

1: Underflow generated

DMAC channel 1 suspend flag (D1SFI)

0: Not suspended

1: Suspended

DMAC transfer suspend control bit (DTSC)

0: Suspending only burst transfers during interrupt

process

1: Suspending both burst and cycle steal transfers

during interrupt process

DMAC register reload disable bit (DRLDD)

0: Enabling reload of source and destination registers

of both channels

1: Disabling reload of source and destination registers

of both channels

Reserved bit (“0” at read/write)

Channel index bit (DCI)

0: Channel 0 accessible

1: Channel 1 accessible

DMAC channel x mode register 1 (address 004016)

DMAxM1

DMAC channel x source register increment/decrement

selection bit (DxSRID)

0: Increment after transfer

1: Decrement after transfer

DMAC channel x source register increment/decrement enable

bit (DxSRCE)

0: Increment/Decrement disabled (No change after transfer)

1: Increment/Decrement enabled

DMAC channel x destination register increment/decrement

selection bit (DxDRID)

0: Increment after transfer

1: Decrement after transfer

DMAC channel x destination register increment/decrement

enable bit (DxDRCE)

0: Increment/Decrement disabled (No change after transfer)

1: Increment/Decrement enabled

DMAC channel x data write control bit (DxDWC)

0: Writing data in reload latches and registers

1: Writing data in reload latches only

DMAC channel x disable after count register underflow

enable bit (DxDAUE)

0: Channel x enabled after count register underflow

1: Channel x disabled after count register underflow

DMAC channel x register reload bit (DxRLD)

0: Not reloaded (Bit is always read as “0”)

1: Source, destination, and transfer count registers contents

of channel x to be reloaded

DMAC channel x transfer mode selection bit (DxTMS)

0: Cycle steal transfer mode

1: Burst transfer mode

DMAC channel 0 hardware transfer request source bits (D0HR)

b3b2b1b0

0 0 0 0: Not used

0 0 0 1: UART receive interrupt

0 0 1 0: UART transmit interrupt

0 0 1 1: Not used

0 1 0 0: INT0 interrupt

0 1 0 1: USB endpoint 1 IN_PKT_RDY signal

(falling edge active)

0 1 1 0: USB endpoint 2 IN_PKT_RDY signal

(falling edge active)

0 1 1 1: Not used

1 0 0 0: USB endpoint 1 OUT_PKT_RDY signal

(rising edge active)

1 0 0 1: USB endpoint 1 OUT_FIFO_NOT_EMPTY signal

(rising edge active)

1 0 1 0: USB endpoint 2 OUT_PKT_RDY signal

(rising edge active)

1 0 1 1: Not used

1 1 0 0: Not used

1 1 0 1: Not used

1 1 1 0: Serial I/O trasmit/receive interrupt

1 1 1 1: Not used

DMAC channel 0 software transfer trigger (D0SWT)

0: No action (Bit is always read as “0”)

1: Request of channel 0 transfer by writing “1” (Note 1)

Reserved bit (“0” at read/write)

DMAC channel 0 transfer initiation source capture

register reset bit (D0CRR)

0: No action (Bit is always read as “0”)

1: Reset of channel 0 capture register by writing “1” (Note 1)

DMAC channel 0 enable bit (D0CEN)

0: Channel 0 disabled

1: Channel 0 enabled (Note 2)

DMAC channel 0 mode register 2 (address 004116)

DMA0M2

DMAC channel 1 hardware transfer request source bits (D1HR)

b3b2b1b0

0 0 0 0: Not used

0 0 0 1: Not used

0 0 1 0: Not used

0 0 1 1: Not used

0 1 0 0: INT1 interrupt

0 1 0 1: USB endpoint 1 IN_PKT_RDY signal

(falling edge active)

0 1 1 0: USB endpoint 2 IN_PKT_RDY signal

(falling edge active)

0 1 1 1: Not used

1 0 0 0: USB endpoint 1 OUT_PKT_RDY signal

(rising edge active)

1 0 0 1: USB endpoint 1 OUT_FIFO_NOT_EMPTY signal

(rising edge active)

1 0 1 0: USB endpoint 2 OUT_PKT_RDY signal

(rising edge active)

1 0 1 1: Not used

1 1 0 0: Not used

1 1 0 1: Not used

1 1 1 0: Timer 1 trasmit/receive interrupt

1 1 1 1: Not used

DMAC channel 1 software transfer trigger (D1SWT)

0: No action (Bit is always read as “0”)

1: Request of channel 0 transfer by writing “1” (Note 1)

Reserved bit (“0” at read/write)

DMAC channel 1 transfer initiation source capture

register reset bit (D1CRR)

0: No action (Bit is always read as “0”)

1: Reset of channel 1 capture register by writing “1” (Note 1)

DMAC channel 1 enable bit (D1CEN)

0: Channel 0 disabled

1: Channel 0 enabled (Note 2)

DMAC channel 1 mode register 2 (address 004116)

DMA1M2

b0

b7

b0

b7

b0

b7

b0

b7

Notes 1: This bit is automatically cleared to “0” after writing “1”.

2: When setting this bit to “1”, simultaneously set the DMAC channel x transfer initiation source capture register reset bit (bit 6 of DMAxM2) to “1”.

0

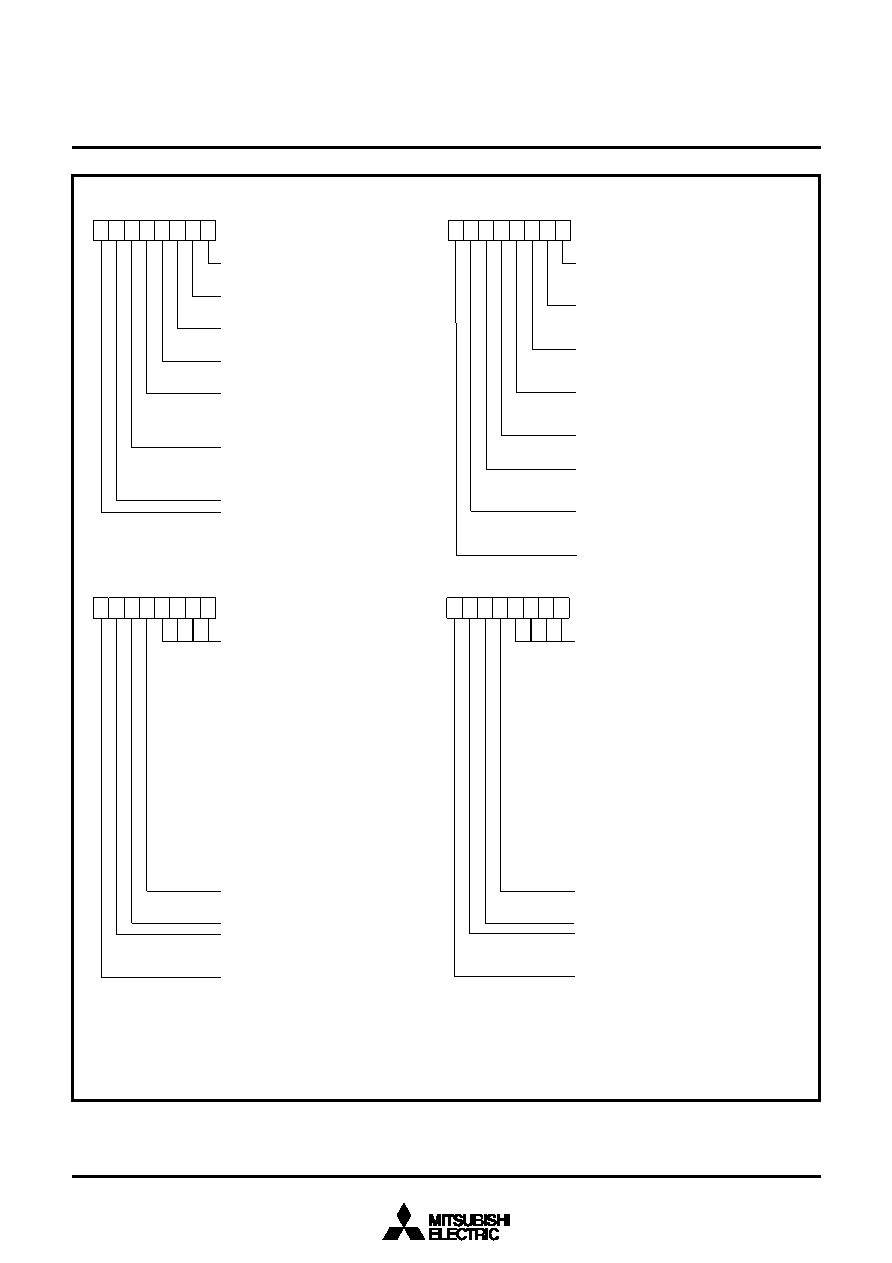

Fig. 30 Structure of DMACx related register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37643M8-XXXHP | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP80 |

| M37702S1LGP | 16-BIT, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37702M2LXXXGP | 16-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37702M2LXXXHP | 16-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37703MDBSP | 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PDIP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37643F8M8-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37643M8E8-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37643M8M8-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M3764A-12 | 制造商:OK International 功能描述: |

| M3765 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:HORN/SIREN WITH SOFT CHIRP 6 ALARM SOUNDS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。