- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69013 > M37274MA-XXXSP 8-BIT, MROM, MICROCONTROLLER, PDIP52 PDF資料下載

參數(shù)資料

| 型號: | M37274MA-XXXSP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, MICROCONTROLLER, PDIP52 |

| 封裝: | 0.600 INCH, 1.778 MM PITCH, SHRINK, PLASTIC, DIP-52 |

| 文件頁數(shù): | 114/131頁 |

| 文件大小: | 2049K |

| 代理商: | M37274MA-XXXSP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁當前第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁

83

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER

and ON-SCREEN DISPLAY CONTROLLER

M37274MA-XXXSP

PRELIMINARY

Notice:

This

is not

a final

specification.

Some

paramentic

limits

are

subject

to change.

MITSUBISHI MICROCOMPUTERS

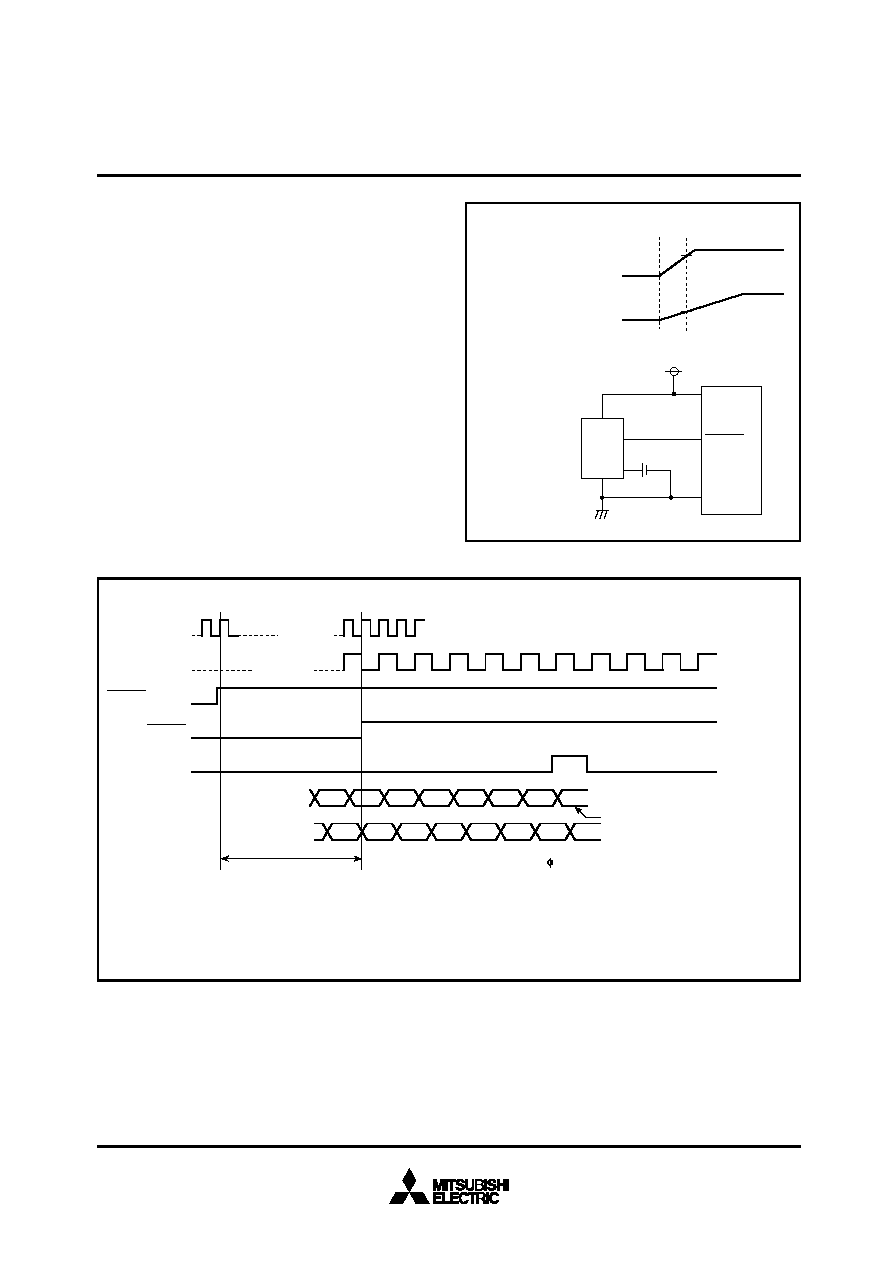

RESET CIRCUIT

When the oscillation of a quartz-crystal oscillator or a ceramic reso-

nator is stable and the power source voltage is 5 V

± 10 %, hold the

______

RESET pin at LOW for 2

s or more, then return is to HIGH. Then, as

shown in Figure 94, reset is released and the program starts form

the address formed by using the content of address FFFF16 as the

high-order address and the content of the address FFFE16 as the

low-order address. The internal state of microcomputer at reset are

shown in Figures 5 to 9.

An example of the reset circuit is shown in Figure 93.

The reset input voltage must be kept 0.9 V or less until the power

source voltage surpasses 4.5 V.

Fig. 94. Reset Sequence

Fig. 93. Example of Reset Circuit

Power source voltage 0 V

Reset input voltage 0 V

4.5 V

0.9 V

Poweron

26

30

27

Vcc

RESET

Vss

M37274MA-XXXSP

1

5

4

3

0.1

F

M51953AL

XIN

φ

RESET

Internal RESET

SYNC

Address

Data

32768 count of XIN

clock cycle (Note 3)

Reset address from the vector table

?

01, S

01, S-1 01, S-2

FFFE

FFFF

ADH,

ADL

?

ADL

ADH

Notes 1 : f(XIN) and f(

) are in the relation : f(XIN) = 2f (

φ).

2: A question mark (?) indicates an undefined state that

depends on the previous state.

3 : Immediately after a reset, timer 3 and timer 4 are

connected by hardware. At this time, “FF 16” is set

in timer 3 and “0716” is set to timer 4. Timer 3 counts down

with f(XIN

)/16, and reset state is released by the timer 4

overflow signal.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37373M8-XXXSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP52 |

| M37409M2-XXXFP | 8-BIT, MROM, 10 MHz, MICROCONTROLLER, PQFP56 |

| M37413E6HXXXFP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37413M4-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M37420M4-XXXSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP52 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37276MF248SP | 制造商:MITSUBISHI 功能描述:* |

| M37276MF2575P | 制造商:MITSUBISHI 功能描述:* |

| M37276MF260SP | 制造商:MITSUBISHI 功能描述:* |

| M37276MF300SP | 制造商:MITSUBISHI 功能描述:* |

| M37276MF301SP | 制造商:MITSUBISHI 功能描述:* |

發(fā)布緊急采購,3分鐘左右您將得到回復。