- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67761 > M32000D4BFP-80 32-BIT, 80 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | M32000D4BFP-80 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 80 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | 14 X 20 MM, 0.65 MM PITCH, PLASTIC, LQFP-100 |

| 文件頁數(shù): | 19/44頁 |

| 文件大小: | 448K |

| 代理商: | M32000D4BFP-80 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

SINGLE-CHIP 32-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

M32000D4BFP-80

26

M32000D4BFP-80

(master)

ROM

ASIC

PP0

M/S

HREQ

INT

M32000D4BFP-80

(slave)

HACK

HREQ

HACK

bus

arbiter

INT

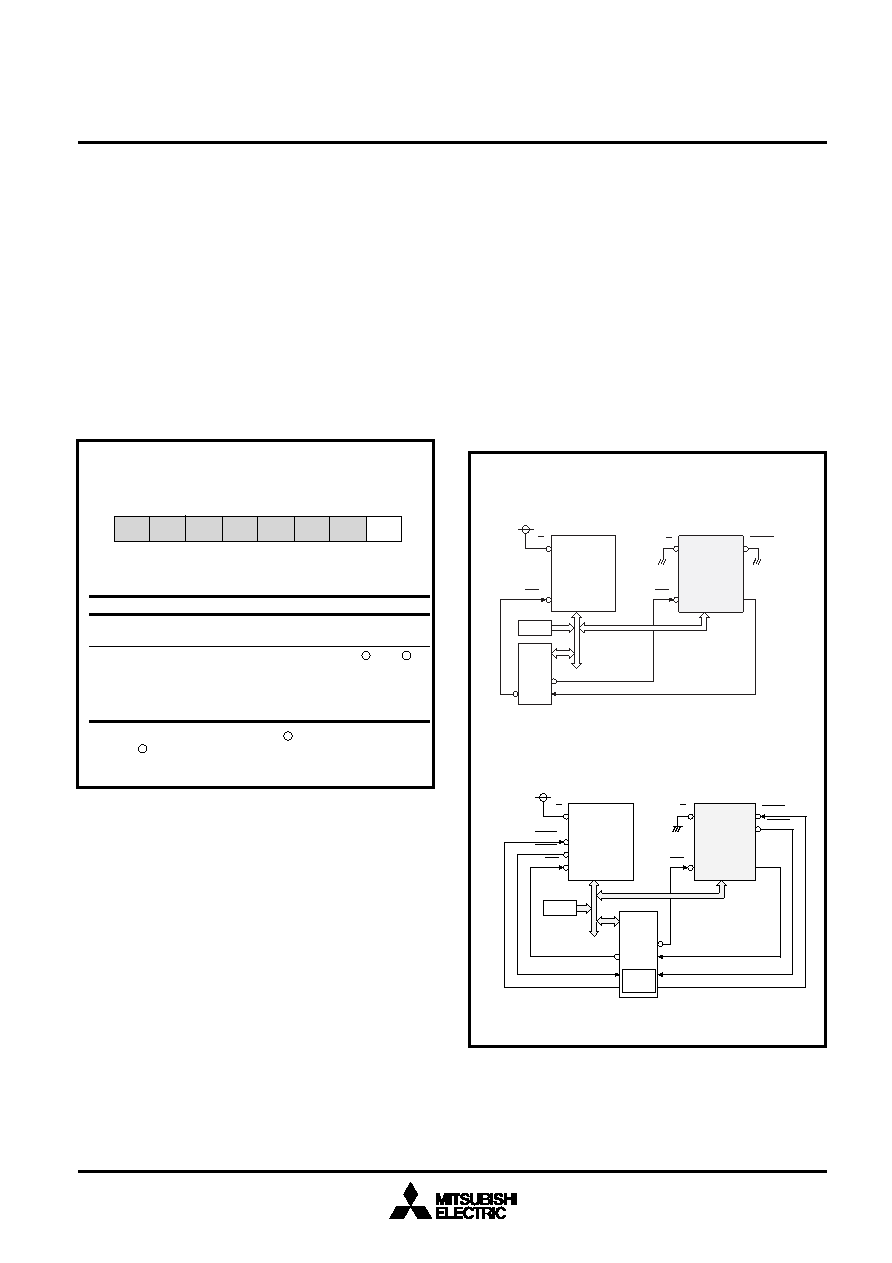

Master/slave mode

_

The M32000D4BFP-80 has an M/S (master/slave) pin for multipro-

cessor configuration use.

_

master mode (M/S = "H")

_

This is normal operation mode. Set the M/S pin to an "H" level. It is

used when the M32000D4BFP-80 is used as the main CPU in a

system.

_

slave mode (M/S = "L")

This operation mode is for when the M32000D4BFP-80 is used as a

_

coprocessor. Set the M/S pin to an "L" level. When set to slave mode,

the M32000D4BFP-80 does not start operation even after a reset,

until an interrupt request or the SBI is input. Processing is carried out

by communicating with the master M32000D4BFP-80, using the two

programmable I/O ports and the external interrupt signal.

D24

D25

D26

D27

D28

D29

D30

D31

LM

lock control register (MLCR) < address: H'FFFF FFF7>

Fig. 26 Lock control register

______

0: HREQ

exclusive

lock mode

___

1: CS exclusive

lock mode

R = 0 ... "0" when reading

R =

... read enabled

W =

... write enabled

W =

: write disabled

<at reset: H'00>

D

bit name

function

R

W

24 - 30

Not

0

!

assigned.

31

LM

(lock mode)

Coprocessor only configuration example

The slave M32000D4BFP-80 accesses only the internal DRAM and

_

_____

never the external bus. M/S and HREQ are fixed at the "L" level. The

slave M32000D4BFP-80 executes the instructions that the master

M32000D4BFP-80 downloads to the internal DRAM. The data trans-

fer request (processing complete) from the slave M32000D4BFP-80

is notified to the master M32000D4BFP-80 by inputting the interrupt

request via the programmable I/O port. The data transaction is car-

ried out when the master M32000D4BFP-80 accesses the internal

DRAM in the slave M32000D4BFP-80.

Common bus coprocessor configuration example

In this configuration, the slave M32000D4BFP-80 can also access

the external bus. Communications between the master and slave

CPUs is carried out using the programmable I/O ports and the inter-

rupt request input.

<coprocessor only configuration>

<common bus coprocessor configuration>

Fig. 27 Master/slave system configuration example

M32000D4BFP-80

(master)

ROM

ASIC

INT

PP0

M/S

HREQ

INT

M32000D4BFP-80

(slave)

no access to

external bus

!

相關PDF資料 |

PDF描述 |

|---|---|

| M32171F4VFP | 32-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP144 |

| M32171F3VFP | 32-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP144 |

| M32173F2VFP | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP144 |

| M32172F2VFP | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP144 |

| M32186F8VFP | 32-BIT, FLASH, 80 MHz, RISC MICROCONTROLLER, PQFP144 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M32002AGLJ | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AGMJ | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AGPJ | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AMLJ | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

| M32002AMMJ | 制造商:MTRONPTI 制造商全稱:MTRONPTI 功能描述:9x14 mm, 3.3/2.5/1.8 Volt, PECL/LVDS/CML, VCXO |

發(fā)布緊急采購,3分鐘左右您將得到回復。