- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT971ABE LAN TRANSCEIVER|SINGLE|CMOS|BGA|64PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT971ABE |

| 英文描述: | LAN TRANSCEIVER|SINGLE|CMOS|BGA|64PIN|PLASTIC |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器|單|的CMOS | BGA封裝| 64管腳|塑料 |

| 文件頁數(shù): | 41/68頁 |

| 文件大?。?/td> | 1177K |

| 代理商: | LXT971ABE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Low-Power Octal PHY

—

LXT9784

Datasheet

41

The BP4B5B pin and bit 14 in PHY register 11

’

h are ORed together. This pin bypasses the 4B5B

encoder/decoder in the transmit and receive sections. In 4B5B bypass mode the data is transmitted

in 5-bit symbols. In RMII mode, the fifth bit (MSB) of all eight ports is driven through the TXD4

pin. The TXD4 pin is a static pin and should be pulled up or pulled down. In SMII mode, TXER

represents the fifth bit.

2.6.5

SCRMBP

(Scrambler Bypass)

In order to enter scrambler by-pass this pin must be set high after the end of reset. During reset this

pin must be pulled-down to ensure proper operation of the LXT9784.

The SCRMBP pin and bit 15 in PHY register 11'h are ORed together.

2.7

PHY Addresses

The ID<1:0> pins are used to set the PHY addresses for the MII management interface.

The PHYs are assigned consecutive addresses in increasing order, starting with PHY0. The address

of PHY0 is determined by the setting of ID<1:0>. This allows up to

four LXT9784s to be connected on a single MII management bus. Up to thirty-two ports are

available when using all the combinations of ID<1:0>.

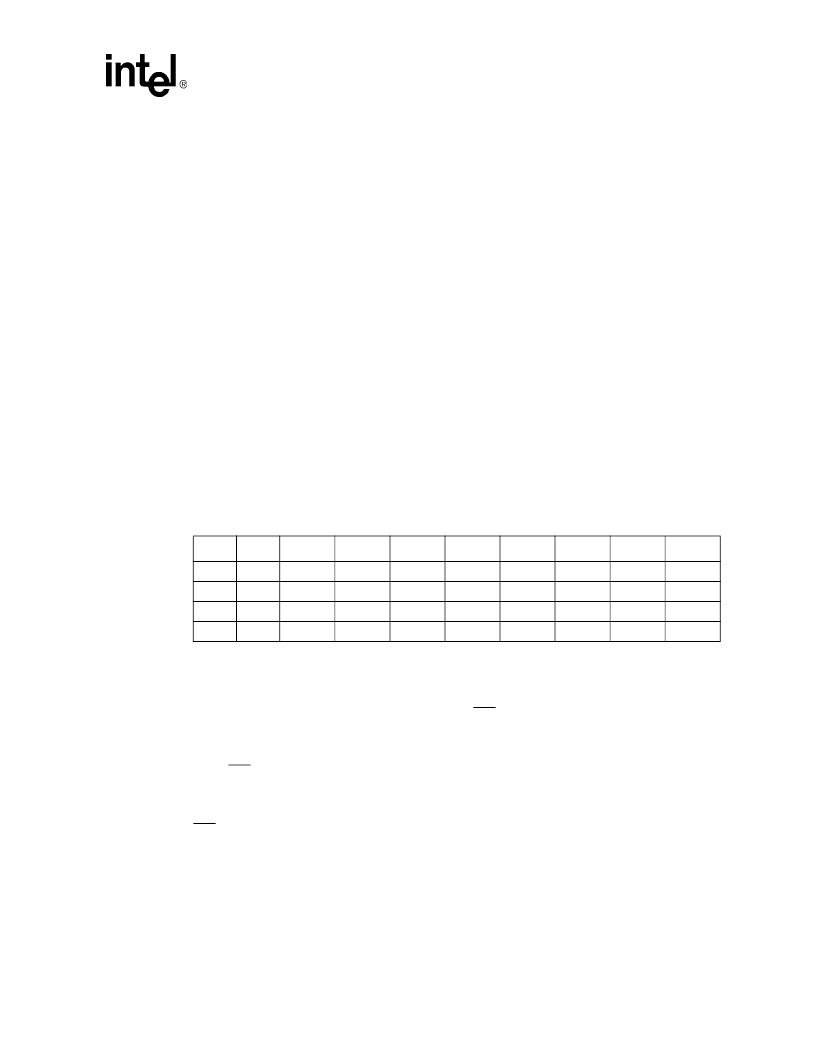

Table 16

shows the internal PHY addresses

for each of the possible combinations of ID<1:0>.

2.8

Link Status Interrupt

The LXT9784 provides an open-drain interrupt pin (INT), which is driven low by the LXT9784

when one or more of it

’

s internal PHYs has a change in link status.

Figure 11

is a simplified

diagram of the interrupt structure.

When INT is driven low, all of the PHY interrupt registers should be read, to determine which port

or ports caused the interrupt (Refer to Table 51). Once a PHY interrupt bit has been read, it is self-

cleared. The interrupt line becomes inactive only after reading the Link Status Interrupt bits of all

the PHYs that caused the interrupt. In the case of more than one PHY having an interrupt pending,

INT remains asserted until after reading the last PHY with a Link Status Interrupt bit set to

“

1

”

.

If during the procedure of reading the interrupt registers a new change of link status occurred on a

PHY which has already been accessed, the interrupt line remains asserted after completing the read

procedure.

This feature can be used instead of polling the PHYs for link status change.

Table 16. PHY Addresses

ID_1

ID_0

PHY0

PHY1

PHY2

PHY3

PHY4

PHY5

PHY6

PHY7

0

0

00000

00001

00010

00011

00100

00101

00110

00111

0

1

01000

01001

01010

01011

01100

01101

01110

01111

1

0

10000

10001

10010

10011

10100

10101

10110

10111

1

1

11000

11001

11010

11011

11100

11101

11110

11111

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT971ALC | LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC |

| LXT971ALE | LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC |

| LXT974QC | LAN Transceiver |

| LXT975QC | LAN Transceiver |

| LXT9761 | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT971ALC | 制造商:Intel 功能描述:LAN Transceiver, Single, 64 Pin, Plastic, QFP 制造商:Intellon Corporation 功能描述:LAN Transceiver, Single, 64 Pin, Plastic, QFP 制造商:Level One 功能描述:LAN Transceiver, Single, 64 Pin, Plastic, QFP |

| LXT971ALE | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3V Dual-Speed Fast Ethernet PHY Transceiver |

| LXT971LC | 制造商:Intel 功能描述: |

| LXT972A | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3V Dual-Speed Fast Ethernet Transceiver Datasheet |

| LXT972ALC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3V Dual-Speed Fast Ethernet Transceiver Datasheet |

發(fā)布緊急采購,3分鐘左右您將得到回復。