- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369872 > LU5X34F Quad Gigabit Ethernet Transceiver PDF資料下載

參數(shù)資料

| 型號: | LU5X34F |

| 英文描述: | Quad Gigabit Ethernet Transceiver |

| 中文描述: | 四個千兆以太網(wǎng)收發(fā)器 |

| 文件頁數(shù): | 22/26頁 |

| 文件大小: | 445K |

| 代理商: | LU5X34F |

22

Lucent Technologies Inc.

LU5X34F

Quad Gigabit Ethernet Transceiver

Preliminary Data Sheet

July 2000

Test Modes

Note:

Test modes are intended for manufacture test only and are not guaranteed to be operational. They may be

modified or eliminated without prior notice.

The device has per-channel test modes as well as global test modes. The bypass PLL, BYPPLL, is a global test

input because it modifies the operation of the analog PLL. Test bits TEST[4:1] generally operate in the localized

mode. The LDST[A:D] inputs are enable signals that permit the TEST[4:1] signals to be injected into a particular

channel.

For example, if LDSTA = 1, the TEST[4:1] signals directly control the test modes in the A channel. Once

LDSTA = 0, the previous values of TEST[4:1] are held for the A channel. The TEST[4:1] signals control the four

channels (A, B, C, D) via level sense latches that are gated with the LDST[A:D] inputs. TEST[5] is a global test pin

used for both injection of signals as well as for monitoring points within the device.

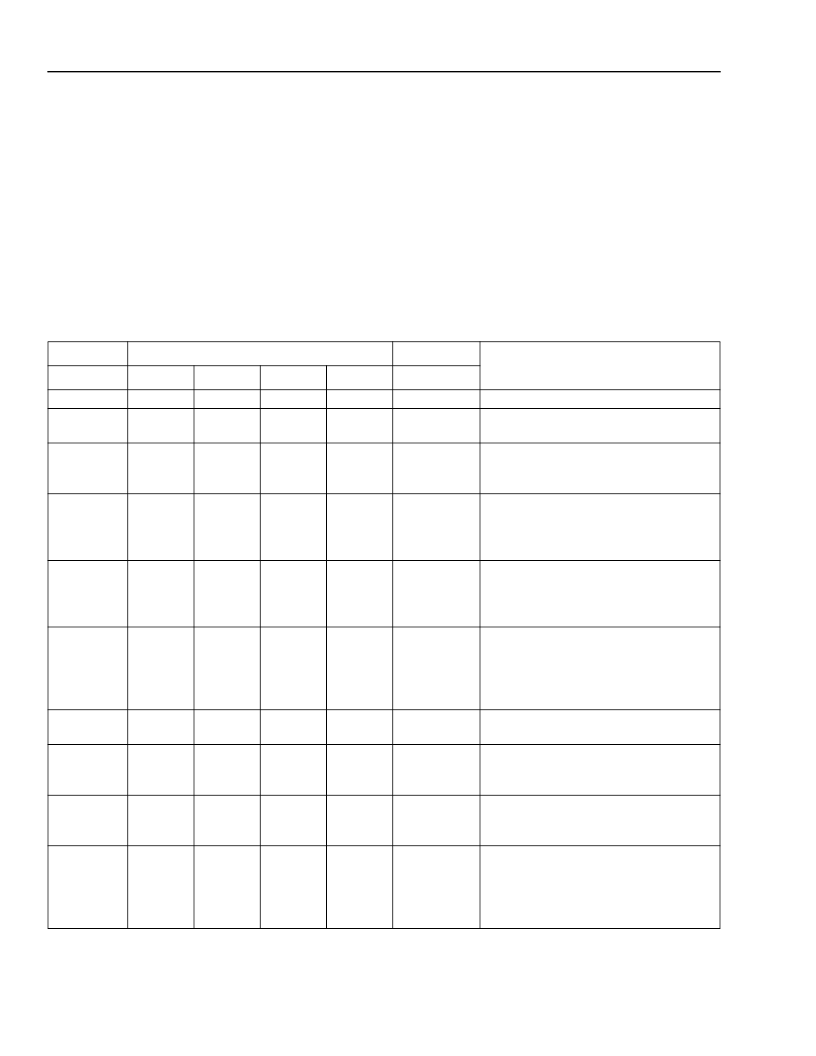

Table 18. Test Modes

Global

Local Test Configuration

Global

Operation

BYPPLL

0

0

TEST1

1

1

TEST2

1

1

TEST3

1

1

TEST4

1

0

TEST5

X

Output

Normal operation.

Analog PLL feedback signal viewed at

TEST5 pin.

Transceiver operates normally except

RX[9:0] output is from digital filter, not

the serial data.

Transceiver operates normally except

RX[9:0] output is from digital filter and

the analog PLL feedback signal is

viewed at TEST5 pin.

Digital filter forced to count. Pulses

applied at TEST4 increment accumula-

tor; pulses at TEST5 decrement accu-

mulator.

RX[9:0] output is from digital filter, not

the serial data. Digital filter forced to

count. Pulses applied at TEST4 incre-

ment accumulator; pulses at TEST5

decrement accumulator.

Parallel loopback. TX[9:0] = RX[9:0].

RX[9:0] remains active.

Parallel loopback. TX[9:0] = RX[9:0]

and analog PLL feedback signal viewed

at TEST5 pin. RX[9:0] remains active.

RX[9:0] output is from digital filter, not

the serial data. Receive channel is held

in reset. BYPPLL overrides this reset.

RX[9:0] output is from digital filter, not

the serial data. Receive channel is held

in reset. BYPPLL overrides this reset.

Analog PLL feedback signal viewed at

TEST5 pin

0

1

1

0

1

X

0

1

1

0

0

Output

0

1

0

1

P

P

0

1

0

0

P

P

0

0

1

1

1

X

0

0

1

1

0

Output

0

0

1

0

1

X

0

0

1

0

0

Output

相關PDF資料 |

PDF描述 |

|---|---|

| LU5X34F | Quad Gigabit Ethernet Transceiver(千兆位以太網(wǎng)四收發(fā)器) |

| LUCL8551AAU | Subscriber Line Interface Circuit |

| LUCL8551AP | Subscriber Line Interface Circuit |

| LUCL8560AAU | Subscriber Line Interface Circuit |

| LUCL8560AU | Subscriber Line Interface Circuit |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LU5Y041XLF | 制造商:BOTHHAND 制造商全稱:Bothhand USA, LP. 功能描述:1×5 RJ45 CONNECTOR MODULE WITH INTEGRATED 10/100 BASE-TX MAGNETICS |

| LU6000F0 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:16-Bit Single-Chip Microcomputers (With Built-In Flash Memory) |

| LU6000F1 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:16-Bit Single-Chip Microcomputers (With Built-In Flash Memory) |

| LU600Z | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:GREEN OVAL LAMP LED |

| LU601 | 制造商:SEOUL 制造商全稱:Seoul Semiconductor 功能描述:BLUE OVAL LAMP LED |

發(fā)布緊急采購,3分鐘左右您將得到回復。