- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358798 > LH540215 (Sharp Corporation) 512 x 18 / 1024 x 18 Synchronous FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | LH540215 |

| 廠商: | Sharp Corporation |

| 英文描述: | 512 x 18 / 1024 x 18 Synchronous FIFO |

| 中文描述: | 512 ×一千〇二十四分之一十八× 18同步FIFO |

| 文件頁(yè)數(shù): | 6/48頁(yè) |

| 文件大小: | 423K |

| 代理商: | LH540215 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

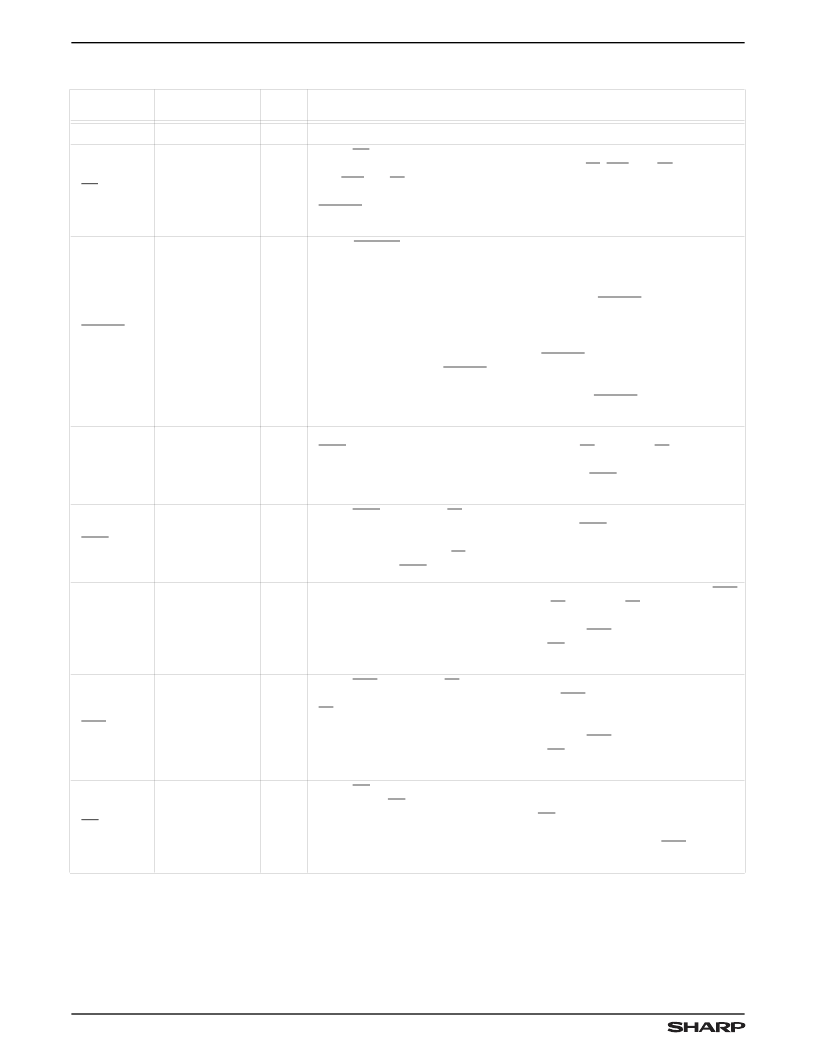

PIN DESCRIPTIONS

PIN

NAME

PIN

TYPE

1

DESCRIPTION

D

0

– D

17

Data Inputs

I

Data inputs from an 18-bit bus.

RS

Reset

I

When RS is taken LOW, the FIFO’s internal read and write pointers are set to

address the first physical location of the RAM array; FF, PAF, and HF go HIGH;

and PAE and EF go LOW. The programmable-flag-offset registers

and the

Control Register

are set to their default values. (But see the description of

EMODE

, below.) A reset operation is required before an initial read or write

operation after power-up.

EMODE

Enhanced

Operating

Mode

I

When EMODE is tied LOW, the default setting for Control Register bits 00-05

after a reset operation changes to HIGH rather than LOW, thus enabling all

Control-Register-controllable Enhanced Operating Mode features, and

allowing access to the Control Register for reprogramming or readback.

(See Tables 1, 2, and 5.) If this behavior is desired, EMODE may be

grounded; however, Control Register bits 00-05 still may be individually

programmed to selectively enable or disable certain of the Enhanced Mode

features, even though those features associated with interlocked-paralleled

operation always are enabled whenever EMODE is being asserted. (See

Table 2.) Alternatively, EMODE may be tied to V

CC,

so that the FIFO is

functionally IDT-compatible, and the Control Register is not accessible or

visible, and all of its bits remain LOW.

Controlling EMODE dynamically

during system operation is not recommended.

WCLK

Write Clock

I

Data is written into the FIFO on a LOW-to-HIGH transition of WCLK, whenever

WEN (Write Enable) is being asserted (LOW), and LD is HIGH. If LD is LOW, a

programmable register rather than the internal FIFO memory is written into.

In the

Enhanced Operating Mode, WEN

2

is ANDed with WEN to produce an

effective internal write-enable signal.

WEN

Write Enable

I

When WEN is LOW and LD is HIGH, an 18-bit data word is written into the FIFO

on every LOW-to-HIGH transition of WCLK. When WEN is HIGH, the FIFO

internal memory continues to hold the previous data. (See Table 3.) Data will not

be written into the FIFO if FF is LOW.

In the Enhanced Operating Mode, WEN

2

is ANDed with WEN to produce an effective internal write-enable signal.

RCLK

Read Clock

I

Data is read from the FIFO on a LOW-to-HIGH transition of RCLK whenever REN

(Read Enable) is being asserted (LOW), and LD is HIGH. If LD is LOW, a

programmable register rather than the internal FIFO memory is read from.

In the

Enhanced Operating Mode, REN

2

is ANDed with REN (and whenever

Control Register bit 05 is HIGH, also with OE) to produce an effective

internal read-enable signal.

REN

Read Enable

I

When REN is LOW and LD is HIGH, an 18-bit data word is read from the FIFO on

every LOW-to-HIGH transition of RCLK. When REN is HIGH, and/or also when

EF is LOW, the FIFO’s output register continues to hold the previous data word,

whether or not Q

0

– Q

17

(the data outputs) are enabled. (See Table 3.)

In the

Enhanced Operating Mode, REN

2

is ANDed with REN (and whenever

Control Register bit 05 is HIGH, also with OE) to produce an effective

internal read-enable signal.

OE

Output Enable

I

When OE is LOW, the FIFO’s data outputs drive the bus to which they are

connected. If OE is HIGH, the FIFO’s outputs are in high-Z (high-impedance)

state.

In the Enhanced Operating Mode, OE not only continues to control the

outputs in this same manner, but also can function as an additional ANDing

input to the combined effective read-enable signal, along with REN and

REN

2

, whenever Control Register bit 05 is HIGH. (See Table 5.)

1

I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

2

The ostensible differences in signal assertiveness are reconciled before ANDing.

BOLD ITALIC = Enhanced Operating Mode

LH540215/25

512 x 18/1024 x 18 Synchronous FIFO

6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH540235 | 2048 x 18 / 4096 x 18 Synchronous FIFOs |

| LH5420 | 256 x 36 x 2 Bidirectional FIFO |

| LH5424-S | 5 mm T1 3/4 LED, Non Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5424-QT | 5 mm T1 3/4 LED, Non Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5424-T | 5 mm T1 3/4 LED, Non Diffused Super-Bright, Hyper-Red GaAIAs-LED |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH540215U-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Synchronous FIFO |

| LH540215U-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Synchronous FIFO |

| LH540215U-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Synchronous FIFO |

| LH540215U-35 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Synchronous FIFO |

| LH540215U-50 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x18 Synchronous FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。